### 中国神学技术大学 University of Science and Technology of China

## 硕士学位论文

作者姓名

夏昊珺

学科专业

计算机系统结构

号师姓名

周学海教授 宫磊 博士

完成时间

二〇二一年五月

# 中国神学技术大学硕士学位论文

#### 轻量级自动机处理器的设计与实现

作者姓名: 夏昊珺

学科专业: 计算机系统结构

导师姓名: 周学海 教授 宫磊 博士

完成时间: 二〇二一年五月二十九日

## University of Science and Technology of China A dissertation for master's degree

## The design and implementation of a lightweight automata processor

Author: Xia Haojun

Speciality: Computer Architecture

Supervisors: Prof. Xuehai Zhou, Dr. Lei Gong

Finished time: May 29, 2021

#### 中国科学技术大学学位论文原创性声明

本人声明所呈交的学位论文,是本人在导师指导下进行研究工作所取得的成果。除已特别加以标注和致谢的地方外,论文中不包含任何他人已经发表或撰写过的研究成果。与我一同工作的同志对本研究所做的贡献均已在论文中作了明确的说明。

作者签名: 夏昊鴻

签字日期: 2021.5.3

#### 中国科学技术大学学位论文授权使用声明

作为申请学位的条件之一,学位论文著作权拥有者授权中国科学技术大学拥有学位论文的部分使用权,即:学校有权按有关规定向国家有关部门或机构送交论文的复印件和电子版,允许论文被查阅和借阅,可以将学位论文编入《中国学位论文全文数据库》等有关数据库进行检索,可以采用影印、缩印或扫描等复制手段保存、汇编学位论文。本人提交的电子文档的内容和纸质论文的内容相一致。

保密的学位论文在解密后也遵守此规定。

☑公开 □保密(\_\_\_年)

作者签名: 夏夏强

签字日期: 2021.5.3

导师签名:

签字日期: 2021.5.31

#### 摘 要

随着信息时代的到来,我们每天都在产生大量的数据。这其中,有大量非结构化的文本数据,例如在因特网上高速传送的网络数据包、日常收发的邮件、基因测序得到的生物基因序列和计算机系统记录的各种日志文件。一方面,我们可能需要出于安全的目的监控某个系统中的文本数据流。比如,我们可以对接收的TCP 网络包进行深度的检测,从而保护计算机系统不被入侵和损坏。另一方面,我们可以从这些文本数据中挖掘很多有价值的信息。例如,通过分析分布式系统的日志文件,我们可以诊断出该系统近期出现的错误。在这些应用中,我们需要在大规模的输入字符流中同时查询和匹配众多指定的模式。这被称为多模式匹配。然而,CPU 和 GPU 不适用于高性能的多模式匹配计算。CPU 和 GPU 在进行多模式匹配计算时将产生大量不可预测的分支跳转和内存访问,这将引发频繁的分支预测失败和 Cache Miss,从而大幅降低处理速度和能效。为了实现更高效的多模式匹配计算,本文基于领域专用架构设计和实现了一款轻量级自动机处理器 LAP。该处理器可使用较少的硬件资源实现高吞吐的多模式匹配计算。

本文的第一项主要工作是: 提供高效的自动机处理器设计方案, 支持快速的 ADFA 执行。基于自动机处理器进行多模式匹配计算时,我们需要将正则表达式 集合编译为对应的有限自动机模型,并随后根据该自动机模型生成该专用处理 器能够识别的二进制程序。在给定正则表达式集合的情况下,如果我们可以生 成存储器空间占用更小的二进制程序,这将意味着我们的自动机处理器可以同 时查找更多的模式串。为了实现该目的,本文实现了对 ADFA 模型(一种增强 的 DFA 模型)的支持。ADFA 模型基于高效的增量存储算法,实现了有效的自 动机模型压缩。因此,基于 ADFA 模型生成的二进制程序也非常小巧。然而,已 有硬件解决方案在运行 ADFA 模型时处理速度却并不理想。在本文,我们提出 的两条专用于 ADFA 模型的硬件指令。为了支持这两条新的指令,我们提出了 新的自动机处理器硬件架构,同时修改了前人提出的编译器算法。实验表明当运 行 ADFA 模型时,LAP 相比于另一款轻量级自动机处理器 UAP 实现了 32% 到 91%的性能提升。不仅如此,我们设计并实现了一个4阶段的无停顿流水线,可 以高效支持 LAP 指令集。我们使用 Verilog 语言实现了 LAP 处理器核心,并将其 以 263 MHz 的主频部署到了 Xilinx Artix-7 FPGA 上。实验也表明,由于使用了 ADFA 模型和高效的编译算法, LAP 的二进制程序存储效率比 IBM 公司的 RegX 加速器和 Micron 公司的 AP 处理器高了 8 倍。

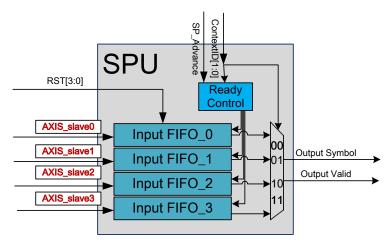

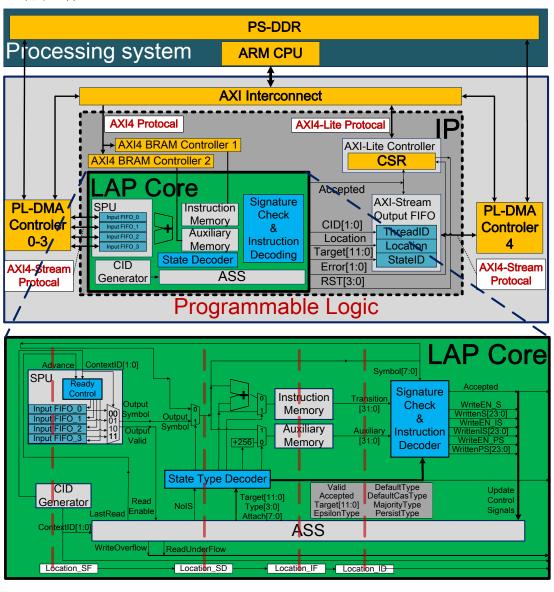

本文的第二项主要工作是:提供完整的设计方案,用于完整地构建基于 LAP 和 ARM CPU 的异构计算片上系统 LAP SoC。该硬件系统主要包含三个部分:以

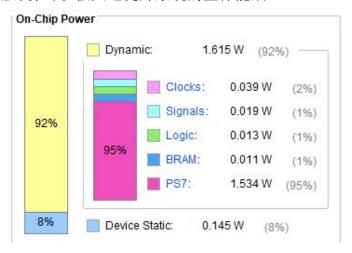

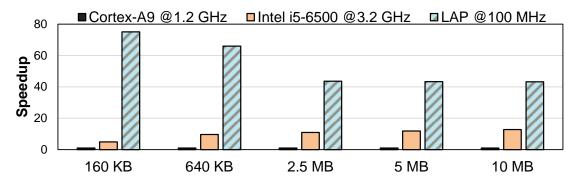

通用处理器为核心的的通用计算系统;由 LAP 核心组成的面向多模式匹配任务的专用计算系统;以及负责大批量数据传输的 DMA 硬件控制器组。该系统可以实际运行在 FPGA 板卡上,并被用来解决生活中实际的多模式匹配问题。不仅如此,LAP\_SoC 具有良好的用户接口。我们在 ARM CPU 系统上部署了 Linux 操作系统,并用 C 语言编写了针对 LAP 和 DMA 控制器的驱动程序。用户只需要具有编写 C 语言的能力,便可以驱动 LAP 核心进行高效的多模式匹配计算。最终,我们将该片上系统部署到了 Zedboard 开发板上。我们发现,在 Zedboard 的双核Cortex-A9 处理器系统上添加一个 LAP 核心,可以在仅增加 5% 功耗的情况下提升 40 多倍面向多模式匹配任务的处理吞吐。

关键词: 模式匹配; 有限自动机; 处理器; 现场可编程逻辑门阵列

#### **ABSTRACT**

With the advent of the information age, we are generating large amounts of data every day. Among them, there are a large amount of unstructured text data, such as network data packets transmitted on the Internet, daily emails sent and received, biological gene sequences, and various log files recorded by computer systems. On the one hand, we may need to monitor the text data in some systems for security purposes. For example, we can perform deep inspections on the received TCP date packets to protect the computer system from intrusion and damage. On the other hand, we can mine valuable information from these text data. For example, by analyzing the log files of a distributed system, we can diagnose recent errors in the system. In these applications, we need to simultaneously search and match many specified patterns in a large-scale character stream, which is called multi-pattern matching. However, CPU and GPU are not suitable for high-performance multi-pattern matching computations. CPU and GPU will generate a large number of unpredictable conditional branches and memory accesses when performing multi-pattern matching computations, which will frequently cause wrong branch predictions and Cache Misses, thereby greatly reducing processing speed and energy efficiency. In order to achieve more efficient multi-pattern matching computations, we designed and implemented a lightweight automata processor LAP based on a domain-specific architecture. This processor can use few hardware resources to achieve high-throughput multi-pattern matching computations.

The first work of this thesis is to provide an efficient automata processor design solution supporting fast ADFA execution. When performing multi-pattern matching computations based on an automata processor, we need to compile the set of regular expressions into a corresponding finite automata model, and then generate a binary program that can be recognized by the dedicated processor. Given a set of regular expressions to be matched, if we can generate a binary program with a smaller memory footprint, our automata processor will be able to search for more patterns simultaneously. In order to achieve this goal, we enabled the support for ADFA model (an enhanced DFA model) in LAP. Incremental storage is enabled in ADFA model, which results in effective compression of the automata model. Therefore, the binary program generated based on the ADFA model is also very small. However, the processing speed of existing hardware solutions is not satisfactory when running ADFA models. To improve this, we propose two new hardware instructions dedicated to the ADFA model. In order to support these

two instructions, we proposed a new hardware architecture for automata processors, and at the same time modified the existing compilation algorithms. Experiments show that compared to another lightweight automata processor UAP, LAP has improved its processing speed by 32% to 91% when they both running ADFA models. What's more, we designed and implemented a 4-stage stall-free pipeline that can efficiently support the LAP instruction set. We implemented the LAP processor core using Verilog language, and deployed it to Xilinx Artix-7 FPGA at 263 MHz. Experiments also show that due to the utilization of ADFA model and the efficient compilation algorithm, the storage efficiency of LAP's binary program is 8× higher than that of IBM's RegX accelerator and Micron's AP.

The second work of this thesis is to provide a complete design of a heterogeneous computing system (LAP\_SoC) based on the LAP core and ARM CPUs. The hardware system mainly includes three parts: a general-purpose computing system; a dedicated computing system for multi-pattern matching tasks composed of LAP cores; and DMA hardware controllers responsible for mass data transmission. The system on chip can actually run on the FPGA board and be used to solve the actual multi-pattern matching problem in real life. Not only that, LAP\_SoC has a good user interface. We deployed the Linux operating system on the ARM CPU system, and wrote drivers for LAP and DMA controllers in C language. Users only need to have the ability to write C language to drive the LAP core to perform efficient multi-pattern matching computations. Finally, we deployed the system-on-chip to Zedboard evaluation board. We found that adding a LAP core to Zedboard's dual-core Cortex-A9 processor system can increase the processing throughput for multi-pattern matching tasks by more than 40× while only increasing power consumption by 5%.

**Key Words**: Pattern Matching; Finite Automata; Processor; Field Programmable Gate Array

#### 目 录

| 第1章    | 绪论                                                        |

|--------|-----------------------------------------------------------|

| 1.1 课  | 题背景及意义                                                    |

| 1.2 相  | <b>关工作</b>                                                |

| 1.2.1  | 基于 DFA 模型的模式匹配引擎 · · · · · · · · · · · · 3                |

| 1.2.2  | 基于 NFA 模型的自动机处理器 · · · · · · · · · · · · 4                |

| 1.2.3  | 专用流水线架构实现并行的模式匹配 · · · · · · · · · · · 6                  |

| 1.2.4  | 广泛支持各类模型的统一自动机处理器 · · · · · · · · · · · · 7               |

| 1.3 本  | 文主要工作・・・・・・・・・・・・・・・・・・・・・・・ 8                            |

| 1.4 论  | 文组织安排・・・・・・・・・・・・・・・・・・・・・・ 9                             |

| 第2章    | 基础理论与部署平台 · · · · · · · · · · · · 10                      |

| 2.1 自  | 动机理论与各类自动机模型 ······10                                     |

| 2.1.1  | DFA 与 NFA 模型·············10                               |

| 2.1.2  | 正则表达式到 NFA 的转化······ 11                                   |

| 2.1.3  | NFA 模型到 DFA 模型的的转化 · · · · · · · · · · · · · · · · · · 12 |

| 2.1.4  | Delayed Input DFA 模型 · · · · · · · · · · · · · · · · · ·  |

| 2.1.5  | ADFA 模型 · · · · · · · · · · · · · · · · · ·               |

| 2.1.6  | 其他的衍生自动机模型 · · · · · · · · · · · · · · · · · · 22         |

| 2.2 ZY | /NQ 的异构计算平台 · · · · · · · · · · · · · · · · · · ·         |

| 2.2.1  | CPU+FPGA 的架构 · · · · · · · · · · · · · · · · · · ·        |

| 2.2.2  | AXI 总线系统······ 24                                         |

| 2.2.3  | AXI4 直接内存访问 · · · · · · · · · · · · · · · · · · ·         |

| 第3章    | LAP: 高效的轻量级自动机处理器核心 · · · · · · · · 27                    |

| 3.1 研  | 究动机 ・・・・・・・・・・・・・・・・・・・・・・・・ 27                           |

| 3.2 LA | AP 的指令集设计·······29                                        |

| 3.2.1  | LAP 的硬件执行模型 · · · · · · · · · · · · · · · · · · ·         |

| 3.2.2  | LAP 指令集 · · · · · · · · · · · · · · · · · · ·             |

| 3.3 LA | AP 指令集优化 · · · · · · · · · · · · · · · · · · ·            |

| 3.3.1  | ADFA 对自动机模型的高效压缩····································      |

| 3.3.2  | ADFA 降低模式匹配速度的根本原因 · · · · · · · · · · · · · · · · · 36   |

| 3.3.3  | ADFA 降低模式匹配速度的优化思路 · · · · · · · · · · · · · · · · · · 37 |

| 3.3.4  | 并行化的 ADFA 执行算法与新的机器指令···································· |

| 3.4 LA | AP 的微体系结构 · · · · · · · · · · · · · · · · · · ·               |

|--------|---------------------------------------------------------------|

| 3.4.1  | 四级流水线架构 · · · · · · · · · · · · · · · · 4                     |

|        | 细粒度多线程・・・・・・・・・・・・・・・・・・43                                    |

| 3.5 编  | 译算法设计与实现・・・・・・・・・・・・・・・・・・ 44                                 |

| 3.5.1  | 将正则表达式集合转化为等价自动机模型 · · · · · · · · · · · · · 45               |

|        | 自动机模型的 Split EffCLiP 二进制表示 · · · · · · · · · · · · · · · · 45 |

| 3.6 实  | 验与评估 · · · · · · · · · · · · · · · · · · ·                    |

| 3.6.1  | LAP 处理速度总览 · · · · · · · · · · · · · · · · · · ·              |

| 3.6.2  | 对 LAP 处理速度的详细评估 · · · · · · · · · · · · · · · · 49            |

| 3.6.3  | LAP 存储效率的分析和讨论······ 50                                       |

| 第4章    | LAP_SoC: 基于 LAP 核心的异构片上系统······ 52                            |

|        | 建 LAP_SoC 的动机······52                                         |

| 4.2 LA | AP 的标准化数据接口 · · · · · · · · · · · · · · · · · · 53            |

| 4.2.1  | 基于 AXI-Stream 的输入接口 · · · · · · · · · · · · · · · · · · ·     |

| 4.2.2  | 基于 AXI-4 的程序写入接口 · · · · · · · · · · · · · · · · · · ·        |

| 4.2.3  | 基于 AXI-Stream 的输出接口 · · · · · · · · · · · · · · · · · · ·     |

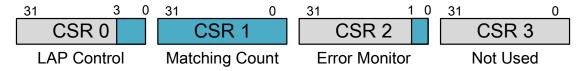

| 4.2.4  | 基于 AXI-Lite 的配置接口····· 55                                     |

|        | AP_SoC 硬件系统······ 55                                          |

| 4.4 LA | AP_SoC 软件系统······ 57                                          |

| 4.4.1  | 操作系统配置与部署 · · · · · · · · · · · · · · · · · · 58              |

|        | 驱动程序设计与实现 · · · · · · · · · · · · · · · · · · ·               |

| 4.5 LA | AP_SoC 部署与评估·······60                                         |

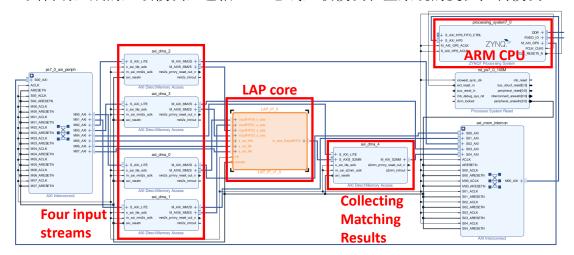

|        | 实现平台与部署结果 · · · · · · · · · · · · · · · · 60                  |

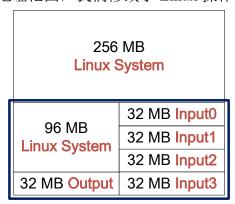

|        | 模式匹配性能的评估方法 · · · · · · · · · · · · · · · · 62                |

| 4.5.3  | 实验结果与性能分析 · · · · · · · · · · · · · · · · · · ·               |

|        | 总结与展望 · · · · · · · · · · · · · · · · · · ·                   |

|        | 文总结 67                                                        |

| 5.2 未  | 来展望 ・・・・・・・・・・・・・・・・・・・・・・・・・ 68                              |

| 参考文献   | ¢69                                                           |

| 致谢 · · |                                                               |

| 在读期值   | ]发表的学术论文与取得的研究成果·········· 76                                 |

#### 插图清单

| 图 1.1  | 本文相关工作的总结・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                    | 3  |

|--------|------------------------------------------------------------------|----|

| 图 1.2  | RegX 硬件加速器处理流程 · · · · · · · · · · · · · · · · · · ·             | 4  |

| 图 1.3  | 基于 RegX 的片上系统结构······                                            | 4  |

| 图 1.4  | Automata Processor 的空间体系结构 · · · · · · · · · · · · · · · · · · · | 5  |

| 图 1.5  | 并行化自动机的执行过程: 枚举所有可能的路径                                           | 7  |

| 图 1.6  | HARE 的硬件流水线结构 · · · · · · · · · · · · · · · · · · ·              | 7  |

| 图 1.7  | UAP 的微体系结构····································                   | 8  |

| 图 1.8  | 基于 UAP 的多核系统·······                                              | 8  |

| 图 2.1  | 正则表达式转化为 NFA 的三条规则 · · · · · · · · · · · · · · · · · · ·         |    |

| 图 2.2  | 示例:正则表达式转化为 NFA ···································              |    |

| 图 2.3  | 需要被转化为 DFA 的 NFA 模型 · · · · · · · · · · · · · · · · · ·          |    |

| 图 2.4  | 子集构建法生成的 DFA 模型 · · · · · · · · · · · · · · · · · ·              | 15 |

| 图 2.5  | DFA 和 $D^2FA$ 模型,接受三个模式: $a+,b+c$ 和 $c*d+\cdots$                 | 16 |

| 图 2.6  | 接受 a+,b+c 和 c*d+ 的 DFA 的空间缩减图 ·····                              | 18 |

| 图 2.7  | 空间缩减图可生成的不同的最大权重生成树 · · · · · · · · · · ·                        |    |

| 图 2.8  | ZYNQ 体系结构总览······                                                | 25 |

| 图 2.9  | AXI DMA 模块框图 · · · · · · · · · · · · · · · · · · ·               | 26 |

| 图 3.1  | LAP 的硬件执行模型····································                  |    |

| 图 3.2  | LAP 的指令格式····································                    |    |

| 图 3.3  | DFA 与等价的 ADFA 模型的状态转换图·········                                  |    |

| 图 3.4  | ADFA 模型对状态转换表的压缩············                                     | 36 |

| 图 3.5  | ADFA 模型的典型拓扑结构····································               |    |

| 图 3.6  | 第一类状态回退的优化方案・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                 |    |

| 图 3.7  | 第二类状态回退的优化方案・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                 |    |

| 图 3.8  | LAP 的四级流水线架构 · · · · · · · · · · · · · · · · · · ·               |    |

| 图 3.9  | 细粒度多线程技术在 LAP 中的应用 · · · · · · · · · · · · · · · · · · ·         |    |

| 图 3.10 | ADFA 模型的层次化结构 · · · · · · · · · · · · · · · · · · ·              |    |

| 图 3.11 | ADFA 模型的 Split EffCLiP 表示 · · · · · · · · · · · · · · · · · ·    |    |

| 图 3.12 | LAP 在 Artix-7 FPGA 上的 Schematic············                      |    |

| 图 3.13 | LAP 在不同工作负载下的总体处理速度·········                                     |    |

| 图 3.14 | 详细的 LAP 性能分析 · · · · · · · · · · · · · · · · · · ·               | 50 |

#### 插图清单

| LAP 的存储效率对比和分析····································                | 51                                                                                                                                                                                                                                                                                                                                      |

|-------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 基于 LAP 的 Xilinx IP 核······                                        | 53                                                                                                                                                                                                                                                                                                                                      |

| LAP 的流式输入接口设计····································                 | 54                                                                                                                                                                                                                                                                                                                                      |

| LAP 计算结果的返回包格式····································                | 55                                                                                                                                                                                                                                                                                                                                      |

| LAP 控制状态寄存器格式····································                 | 55                                                                                                                                                                                                                                                                                                                                      |

| LAP 片上系统整体架构设计····································                | 56                                                                                                                                                                                                                                                                                                                                      |

| ZYNQ 系统的 Block Design · · · · · · · · · · · · · · · · · · ·       | 57                                                                                                                                                                                                                                                                                                                                      |

| <b>ZYNQ</b> 系统的地址分配 · · · · · · · · · · · · · · · · · · ·         | 57                                                                                                                                                                                                                                                                                                                                      |

| ZYNQ 系统 DDR 空间分配 · · · · · · · · · · · · · · · · · · ·            |                                                                                                                                                                                                                                                                                                                                         |

| LAP_SoC 的部署平台: Zedboard 开发板 · · · · · · · · · · · · · · · · · · · | 60                                                                                                                                                                                                                                                                                                                                      |

| LAP 片上系统的层次结构····································                 | 61                                                                                                                                                                                                                                                                                                                                      |

| LAP 片上系统功耗分布 · · · · · · · · · · · · · · · · · · ·                |                                                                                                                                                                                                                                                                                                                                         |

| 桌面 Intel CPU 基于 grep 命令进行多模式匹配 · · · · · · · · · ·                | 63                                                                                                                                                                                                                                                                                                                                      |

| 嵌入式 ARM CPU 基于 grep 命令进行多模式匹配 · · · · · · · · ·                   | 63                                                                                                                                                                                                                                                                                                                                      |

| 使用 LAP 进行多模式匹配····································                | 64                                                                                                                                                                                                                                                                                                                                      |

| LAP 与 Intel 处理器进行模式匹配计算 (不同输入规模下) 的时间                             |                                                                                                                                                                                                                                                                                                                                         |

| 统计 · · · · · · · · · · · · · · · · · · ·                          | 65                                                                                                                                                                                                                                                                                                                                      |

| 三种硬件平台下进行模式匹配计算(不同输入规模下)的加速比 · (                                  | 66                                                                                                                                                                                                                                                                                                                                      |

|                                                                   | 基于 LAP 的 Xilinx IP 核 LAP 的流式输入接口设计 LAP 计算结果的返回包格式 LAP 控制状态寄存器格式 LAP 片上系统整体架构设计 ZYNQ 系统的 Block Design ZYNQ 系统的地址分配 ZYNQ 系统的地址分配 ZYNQ 系统 DDR 空间分配 LAP_SoC 的部署平台: Zedboard 开发板 LAP 片上系统的层次结构 LAP 片上系统的层次结构 LAP 片上系统功耗分布 桌面 Intel CPU 基于 grep 命令进行多模式匹配 嵌入式 ARM CPU 基于 grep 命令进行多模式匹配 使用 LAP 进行多模式匹配 LAP 与 Intel 处理器进行模式匹配计算(不同输入规模下)的时间 统计 |

#### 表格清单

| 表 2.1 | 有 n 个状态的 NFA 和等价 DFA 的存储复杂度和计算复杂度对比···1                      | . 1 |

|-------|--------------------------------------------------------------|-----|

| 表 2.2 | 子集构建法生成的 DFA 模型状态转换表 ····································    | 5   |

| 表 3.1 | LAP 支持的 7 条指令和它们的功能描述····································    | 1   |

| 表 3.2 | LAP 在不同工作负载下的总体处理速度原始数据······4                               | 9   |

| 表 3.3 | 详细的 LAP 性能分析原始数据····································         | 0   |

| 表 3.4 | LAP 的存储效率原始数据····································            | 0   |

| 表 4.1 | 驱动 LAP 的 C 函数 · · · · · · · · · · · · · · · · · ·            |     |

| 表 4.2 | LAP 片上系统总体资源占用····································           | 1   |

| 表 4.3 | 评估性能所使用的三种硬件平台 · · · · · · · · · · · · · 6                   | 2   |

| 表 4.4 | LAP 在不同规模下运行 grep 命令耗时统计···································· | 5   |

| 表 4.5 | Intel 处理器在不同规模下运行 grep 命令耗时统计 · · · · · · · · 6              | 5   |

| 表 4.6 | Cortex-A9 处理器在不同规模下运行 grep 命令耗时统计······6                     | 6   |

| 表 4.7 | 三种硬件平台下进行模式匹配计算的加速比原始数据 · · · · · · · 6                      | 6   |

#### 第1章 绪 论

#### 1.1 课题背景及意义

随着信息时代的到来,我们每天都在产生大量的数据。自从 2011 年开始,"big data"这个词开始广为流传<sup>[1]</sup>。Laney 于 2001 年提出 3Vs(Volume,Variety,和 Velocity)是大数据管理三个维度的挑战<sup>[2]</sup>。随后,该定义作为通用框架被用来描述 big data。Volume 指的是数据规模之大。大数据一般以 TB 和 PB 作为单位进行衡量,而 1TB 可以存储相当于 1500 张 CD 或 220 张 DVD。Velocity 指的是数据生成的速率和它应当被分析和处理的速度。传感器和数字设备(比如智能手机)的广泛使用使得数据以前所未有的速度在产生,被实时处理的需求也带来了极大地挑战。Variety 指的是数据集中数据结构的异构性。结构化数据(关系型数据库或者平展的表格中的数据)仅仅占据现有数据量的 5%<sup>[3]</sup>。事实上,我们每天都在产生大量非结构化的文本数据,比如各类文章、聊天记录、计算机日志、网络流量和基因序列。处理和分析这些文本数据可以帮助我们挖掘一些信息或者出于安全的目的监控某个系统。本文主要研究如何使用专用的硬件处理器进行高效的文本数据处理。

模式匹配被广泛的应用于多种应用领域中,例如网络安全[7],计算生物学[8], 文本数据挖掘 $^{[4][5][6]}$  和计算物理学 $^{[9]}$  等应用。这些应用有一个共同的特征,他 们都需要在大规模的输入字符序列上同时查询和匹配多个指定的子串/模式。例 如,在进行度网络包检测/网络入侵检测时,我们可以通过指定一组恶意代码的 指纹集合,并检测接受的网络包的包头和负载中是否包含这样的恶意代码。基 于这样的目的,很多基于指纹进行深度网络包检测的软件工具应运而生,包括 Snort、Bro 和 ClamAV。然而,在进行深度网络包检测时,针对网络包的扫描速 度需要匹配网络传输速度,也就是要达到 Gbps 的量级。不仅如此,我们需要同 时匹配由几百到上千个正则表达式组成的庞大模式串集合。这些正则表达式可 以是简单的字符串匹配,也可能包括正则表达式支持的通配符(.)和 Kleene 星号 (\*)等运算符。除此以外,生物的基因序列也是一种大数据。在生物学的研究中, 我们需要从海量的生物基因序列中查找特定的基因串。例如,基于 CRISPR/Cas9 免疫系统进行基因编辑是当下非常流行的一种技术。然而在使用该技术时,我们 需要使用 gRNA 来引导 Cas9 核酸酶到达预定的靶点(具有特定的 DNA 序列的 位置)进行基因编辑。值得注意的是,gRNA可以与众多和目标 DNA 序列存在少 量差异的 DNA 序列结合。因此,同一款 gRNA 可以结合的潜在目标靶点非常多。 这导致从庞大的 DNA 链中找出所有的潜在靶点成为了很复杂的计算问题。总的 来说,多模式匹配被广泛的应用于文本数据的处理,而且有着很高的性能需求。

有限自动机(Finite Automata<sup>[13]</sup> 是一个重要的数学概念,也作为一种计算模 型被广泛地用于模式匹配计算。更具体来说,有限自动机可以自然地支持多模式 匹配:同时从主串中查找众多不同的模式。我们可以将要匹配的所有模式串转化 为单个有着特定拓扑结构的有限自动机(该自动机的状态数目和状态间的连接 关系由待匹配的所有模式共同决定)。随后,我们通过运行单个自动机模型,就可 以并行地在大规模输入上同时查找众多的模式。我们熟知的非确定性有限状态 机(Non-deterministic Finite Automata, NFA)和确定性有限状态机 (Deterministic Finite Automata, DFA) 都属于有限自动机这个范畴。除此以外,还有很多新颖的 自动机模型被提出和应用于多个应用场景,包括 AC 自动机和 ADFA 模型[32]。其 中, Aho-Corasick 算法是一款经典的多模式匹配算法。该算法主要靠构造一个 AC 自动机来实现。AC 自动机本质上是一个拓展的确定性有限自动机(DFA), 它支持"失配指针"。通过在一个 trie 树中添加"失配指针", 我们便可以构造出 对应的 AC 自动机。这些额外的"失配指针"允许在查找字符串失败时进行回退 (例如设 Trie 树的单词 cat 匹配失败,但是在 Trie 树中存在另一个单词 cart,失 配指针就会指向前缀 ca),转向某前缀的其他分支,免于重复匹配前缀,提高算 法效率。本文关注的 ADFA 模型吸收了 AC 自动机的思想,实现了更通用的多模 式匹配计算。回顾模式匹配算法的历史,我们可以发现 KMP 算法[10] 和 BM 算 法[11] 是面向单模式串匹配(同时查找和匹配单个模式)的经典算法。然而在上 文提出的应用中,我们则需要同时查找和匹配多个不同模式。对于这样的多模式 匹配任务, 我们当然也可以将它分解为多个单模式匹配任务并串行的执行这些 子任务。但是,这将会非常的低效。由此我们可以看出,基于有限自动机的多模 式匹配算法在本文的目标应用领域中有着不可替代的地位。

通用处理器不适用于高性能的多模式匹配计算。首先,如果我们运行在通用处理器(CPUs 或 GPUs)上模拟自动机模型的执行过程,我们需要重复地根据当前的输入切换当前状态。这会引发大量的不可预测的分支跳转或大量的不规则的内存访问。不可预测的分支预测会导致通用处理器中的分支预测机制失效,引发大量的分支预测失败。紧接着,处理器流水线需要被冲刷和重新执行,从而极大地降低处理器的性能和效率。类似的,不规则的内存访问会引发频繁的缓存缺失(Cache Miss)。这会使得处理器流水线被阻塞,从而降低处理器性能。在过去的十几年中,算法层面的优化被不断提出。这些优化后的模式匹配算法也在CPU和 GPU 上取得了更高的计算吞吐和能效。然而,随着待处理的数据量越来越大,我们对于多模式匹配的计算性能也有了越来越高的需求。但受限于通用处理器自身体系结构的限制,基于传统处理器的多模式匹配计算在性能和能效方面已经无法获得进一步的显著提升。因此近些年,学术界和工业界投入了越来越多的精力去设计和实现专门用于多模式匹配的硬件加速器/自动机处理器。这些

专用硬件相比于传统处理器在性能和能效方面有数量级上的提升。

#### 1.2 相关工作

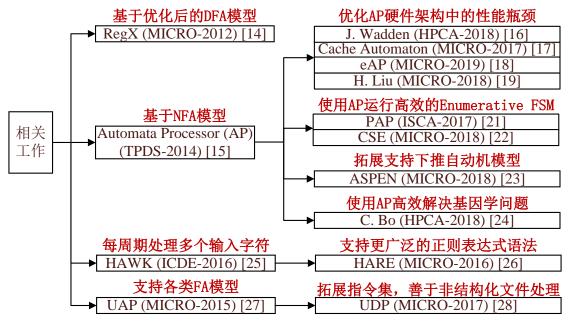

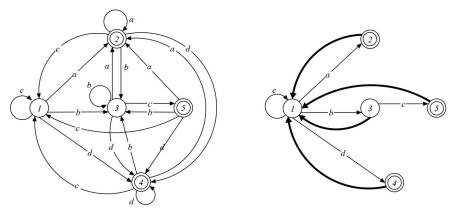

本小节将总结近十年内学术界与工业界提出的面向多模式匹配任务的专用硬件。根据它们所使用的基础架构,这些硬件可以被分类成4类(如图1.1所示)。

图 1.1 本文相关工作的总结

#### 1.2.1 基于 DFA 模型的模式匹配引擎

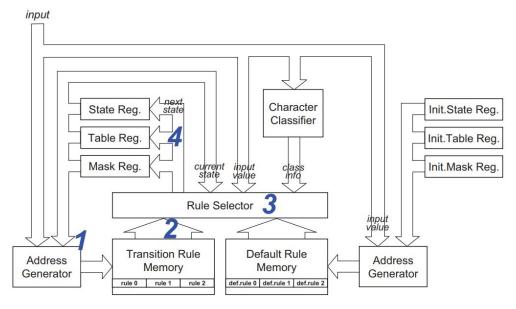

RegX 加速器<sup>[14]</sup> 是由 IBM 公司设计实现的可编程正则表达式匹配引擎,用于进行网络入侵检测。该成果不仅仅发表于体系结构顶级会议上,同时也实际部署在了 IBM 公司的 PowerEN 处理器中。该加速器可以同时匹配上千条模式并实现足以匹配以太网链路带宽的扫描速度(理论扫描速度为 73.6 Gbit/s)。对于典型的网络入侵检测任务,RegX 的实际处理速度达到了 15 到 40 Gbit/s。RegX 的执行流程如图1.2所示,分四步处理每一个输入字符。首先,根据当前状态和当前输入,计算出地址;然后,根据第一步计算出的地址从存储器中取出相应的规则;第三步,从取出的规则中选择需要的部分;第四步,根据取出的规则更新当前状态,实现状态机的一次状态切换。值得一提的是,RegX 需要使用外部 DRAM 来存储其自动机模型(如图1.3),而且内部使用了复杂的 Cache 缓存部分自动机模型。总的来说,该硬件加速器基于拓展的 DFA 模型(名为 B-FSM 模型),实现了较为紧致的存储和非常高速的执行。

图 1.2 RegX 硬件加速器处理流程

图 1.3 基于 RegX 的片上系统结构

#### 1.2.2 基于 NFA 模型的自动机处理器

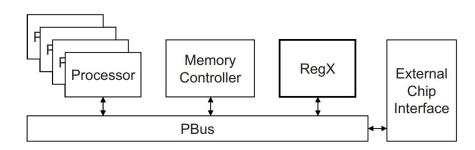

Automata Processor<sup>[15]</sup>(本文简称 AP)是由 Micron 公司设计并生产的基于 NFA 模型的自动机处理器。该处理器可以直接将非确定性有限状态机直接映射 到其空间体系结构上,从而实现大规模的、非常复杂的正则表达式匹配。SDRAM 存储器阵列是当代计算机主存储器的核心结构,而 AP 就是建立在这样的空间架 构下。如图1.4所示,AP 由众多的状态转换元件(STE)构成。这些元件可以并 发的运行从而提供非常高的并行度。通过这个方法,AP 可以提供 NFA 模型所需要的巨大的算力。另一方面,AP 内部使用独热码的方式编码状态机的每个状态。这使得 AP 需要使用 256 个比特去编码一个状态。然而,状态机的状态数会随着 待匹配的正则表达式的数量的增加而增加。当正则表达式总数达到上千条时,状态机状态数也会变得非常巨大。因此,AP 需要占用较大的存储空间。为了解决这个问题,AP 直接使用 SDRAM 阵列存储 NFA 模型,而不是使用 SRAM。通过这个方法,AP 可以存储非常多且非常复杂的正则表达式。相应的,SDRAM 存储阵列也占据了非常多的片上空间和功耗。除了存储阵列,AP 内部还包含一个非常复杂的硬件互联。该硬件互联在图1.4中被称为 Routing Matrix Structure。这

是一种可配置的互联结构,根据要匹配的正则表达式使用不同的方式将 STE 两 两连接起来。总的来说,Automata Processor 是一款非常有名且非常高性能的自 动机处理器。随后,学术界问世了大量基于 AP 架构的自动机处理器。

图 1.4 Automata Processor 的空间体系结构

有一部分研究者试图去分析和优化 AP 存在的性能瓶颈,并在顶级会议上发表了若干篇代表性论文。J. Wadden [16] 通过分析和实验证实,AP 在向宿主处理器汇报匹配结果时存在瓶颈。J. Wadden 等人发现,AP 在运行常见基准测试程序时,会非常频繁的汇报匹配结果;然而,每次汇报的结果数目却很少。因此,他们设计了新的输出压缩策略和新的体系结构专门负责高效的结果汇报。最终,他们相比 AP 实现了 5.1 倍的加速效果。Cache Automaton [17] 修改了 Last-level Cache的结构,在 Cache 上实现了类似 AP 的架构。通过将实现介质从 SDRAM 更换为SRAM,Cache Automaton 相比 AP 实现了显著的功耗降低和性能提升。eAP [18] 优化了 AP 的路由体系结构。具体来说,eAP 优化了 AP 内部的可配置互联结构。通过这种方式,eAP 分别实现了相比 Cache Automaton 和 AP 5.1 倍和 207 倍的计算吞吐的提升。H. Liu [19] 则给 AP 增加了体系结构上的支持,使得新的架构可以支持更大规模的自动机处理。他们发现在运行实际的模式匹配任务时,生成的自动机模型中有大量的状态是永远不会被激活的。然而,这样的状态却会被配

置在 AP 中,同时占据大量的资源。因此,H. Liu 等人预测了这些"无用的"状态,并不将它们配置到处理器中。相应的,他们提出了新的执行机制来处理错误的预测。在经过大量的基准测试后,他们的方案实现了平均 2.1 倍的性能提升。

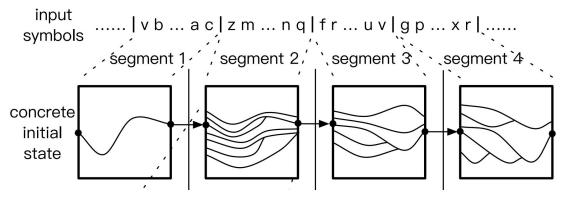

Micron 公司的 AP 被众多研究者应用于并行化单个有限自动机的执行。有 限自动机的执行有着与生俱来的串行依赖: 当前状态 a 根据当前输入的状态会 切换到下一个状态 b, 而下一个状态 b 又会在接受另一个输入后切换到第三个状 态 c。在这个过程中,状态 b 与状态 a 有关,而状态 c 又取决于状态 b。因此,这 样一个计算过程难以被并行化。如图 1.5 所示, T. Mytkowicz<sup>[20]</sup> 提出可以将状态 转换过程切分。除了 segment 1 以外,其他过程都没有确定的开始状态。这是因 为这些过程的开始状态是它们前面一个过程的结束状态。因此,我们需要计算 segment 2 可能存在的每一条状态转换路径。这意味着, segment 2 有多少可能的 开始状态我们就需要计算多少条路径。最终,对于每一个 segment, 我们将从预 先计算的路径中挑选一条路径,并将这些路径拼接起来得到最终的路径。但是, 枚举所有路径带来了额外的计算开销。T. Mytkowicz<sup>[20]</sup> 等人使用了通用处理器 支持的 SIMD 指令进行这些枚举路径的并行计算。PAP<sup>[21]</sup> 首先提出 AP 可以用 于并行化非确定性有限自动机的执行。AP 提供的并行度被利用以实现并行的路 径枚举。同时,各种优化策略被提出用于降低枚举路径所需的计算量。进一步的, CSE<sup>[22]</sup> 提出新的计算原语用于进行更高效的自动机可能路径的枚举。在之前的 工作中,枚举路径的结果是计算出每条路径输入状态到输出状态得映射。在 CSE 中,则是计算一个输入状态集合到输出状态集合的映射。这样的计算原语更适合 AP 的计算架构,因此取得了更高的计算吞吐。总的来说,枚举的方法可以实现 自动机执行过程的串行化,但是也带来了非常高的枚举开销。因此,该项技术主 要面向有计算延迟约束的场景,而不适用于面向高吞吐的模式匹配任务。

AP 也被广泛的应用于解决工业界和学术界的实际问题。ASPEN<sup>[23]</sup> 吸取了先前自动机处理器的设计思想,并增加了对栈进行操作的原语,从而实现了对下推自动机的支持。基于该自动机模型,ASPEN 可以高效执行对树形结构的递归嵌套的语言(例如 Cool,DOT,JSON 和 XML)的解析。C. Bo<sup>[24]</sup> 等人使用 AP 搜索 CRISPR/Cas9 系统下的的潜在 gRNA 脱靶位点。发现这些潜在的位点对进行有效的基因编辑非常重要,但是这一个非常复杂的计算过程。C. Bo 等人提出的基于 AP 的方案,相比 CPU 和 GPU 分别实现了 900 倍和 120 倍的加速比。可以看到,自动机处理器有着日益广泛的应用场景。

#### 1.2.3 专用流水线架构实现并行的模式匹配

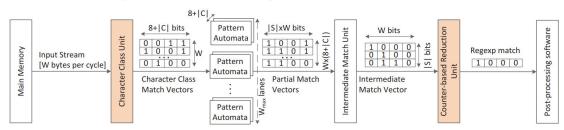

HARE<sup>[25]</sup> 是一款比较特殊的模式匹配处理器,它为文本和非结构化数据的处理提供了强大而灵活的工具。HARE 可以实现超高的模式匹配吞吐量。它的

图 1.5 并行化自动机的执行过程: 枚举所有可能的路径

目标是匹配当下计算机系统的主存带宽(非常大),而不是匹配计算机系统的输入输出带宽。HARE 最特殊的地方在于,它可以在一个时钟周期内同时处理 32 个输入字符,而之前我们提及的各种自动机专用硬件最快只能一个周期处理一个字符。HARE 和它的前身 HAWK<sup>[26]</sup>一样,拥有不会停顿的流水线结构,使用bit-split 自动机模型实现模型压缩,还可以同时处理一个窗口内的全部输入字符。HARE 的流水线结构如图1.6所示。通过增加 Counter-based Reduction Unit,HARE 提供了对正则表达式中 Kleene Star(\*)的支持。总的来说,HAWK 和 HARE 是一类高吞吐的模式匹配加速器;HARE 相比 HAWK 可以支持更加广泛的正则表达式语法,因此拥有更广泛的应用场景。

图 1.6 HARE 的硬件流水线结构

#### 1.2.4 广泛支持各类模型的统一自动机处理器

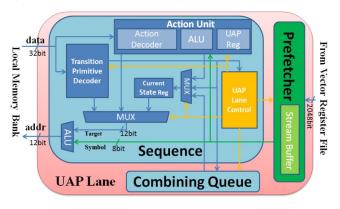

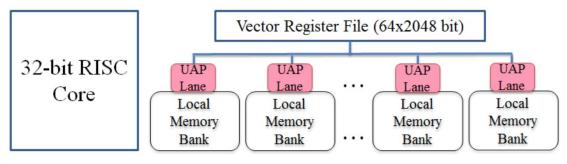

除了经典的 DFA 和 NFA 之外,研究人员提出了越来越多新的自动机模型。这些新颖的自动机模型往往对于某一类的计算负载有着显著地裨益。但是,却没有哪一个自动机模型适用于所有的正则表达式集合。因此,UAP<sup>[27]</sup> 提出了统一的自动机处理器,广泛地支持各类自动机模型(包括 DFA.NFA.ADFA.JFA 等)。

为了实现通用自动机模型所需要的各种底层机制,UAP实现了对应的状态转换原语和对寄存器的操作原语。其中,每条原语对应于 UAP 的一条硬件指令。UAP 的微体系结构如图1.7所示。对于每种自动机模型,Combining Queue 负责存储所有被激活的自动机状态。UAP 每个周期从 Combining Queue 中取出一个激活状态,并从 Prefetcher 中取出当前要处理的字符。随后,UAP 计算出下一条

机器指令的地址。该条机器指令将用于更新当前自动机状态。同时,Action Unit 可以实现对 UAP 内部寄存器的修改,从而实现更复杂的自动机模型。UAP 系统中包含了一个 RISC 的通用处理器核心和 64 个 UAP 核心(如图1.8所示)。每个 UAP 核心平均每周期可以处理一条状态转换原语和寄存器操作。同时,每个 UAP 核心拥有一个片上存储器 Bank,用来存储各自要运行的自动机模型。

图 1.7 UAP 的微体系结构

图 1.8 基于 UAP 的多核系统

UDP<sup>[28]</sup> 建立在 UAP 的架构上,同时增加了对更多指令的支持。通过这种方法,UDP 可以高效的进行分支频繁的计算任务,例如 CSV 文件解析、霍夫曼编解码、模式匹配和 Snappy 压缩解压。

#### 1.3 本文主要工作

本文致力于提出并实现一种轻量级、高性能的自动机处理器。该轻量级处理器可以通过 FPGA 或者 ASIC 平台实现,并与通用 CPU 形成多核异构计算系统,从而实现高吞吐高能效的多模式匹配计算。本文的工作主要包含两个部分:

#### (1) LAP: 更快的面向多模式匹配任务的轻量级自动机处理器

• 通过利用新颖的 ADFA 模型和高效的模型存储算法,LAP 实现了非常高的存储效率,LAP 可以将整个自动机模型压缩存储到有限大小的 SRAM 中,从而不依赖于外部 DRAM 独立的运行。另外,借助于软硬件协同设计的方

- 法,我们并行了 ADFA 模型的执行算法,从而极大的提高了 LAP 的执行速度。在本文中,我们通过 C++ 和 Python 代码实现了相应的编译算法。

- 我们设计了一个 4 阶段流水线, 用于在 FPGA 和 ASIC 上部署高主频的 LAP 核心。为了实现一个无停顿的流水线, 我们使用细粒度多线程技术化解了流水线内部的相关。

- 我们使用 Verilog 语言实现了 LAP 核心,并将其部署到 Xilinx 公司的 Artix-7 FPGA 芯片上。最终, LAP 可以运行在 263 MHz 的主频下。实验结果表明 LAP 相比于 IBM 公司的 RegX 加速器和 Micron 公司的 AP 处理器的存储效率高了 8 倍。同时,相比其他的轻量级自动机处理器,我们的处理器实现了 32% 到 91% 的性能提升。

#### (2) LAP SoC: 基于 LAP 核心的高能效异构计算片上系统实现

- 为了便于将 LAP 核心与 Xilinx FPGA 内的 ARM 处理器集成在一起,我们首先为 LAP 设计并实现了基于 AXI 标准数据接口。然后,我们将 LAP 封装成独立的 IP 核。之后,我们使用 Vivado 的 Block Design 功能,设计并实现了 ARM CPU 和单 LAP 核心的异构计算系统。

- 我们为 LAP 核心和 DMA 控制器编写了相应的 CPU 端驱动程序,驱动 LAP 核心进行模式匹配计算。在多种计算负载下,LAP\_SoC 取得了相比于 Cortex-A9 处理器 40+ 倍和相比于 Intel Core-I5 处理器 3+ 倍的性能提升。

#### 1.4 论文组织安排

本文的第一章已经介绍了自动机处理器的应用场景和相关工作。第二章将详细介绍与 LAP 的设计和实现密切相关的基础知识,包括自动机理论和 LAP\_SoC 的部署平台(ZYNQ FPGA)。第三章作为本文的第一项核心工作,将主要讲述 LAP 高能效核心的设计与实现,从指令集设计,到指令集优化,再到流水线设计和编译器实现。通过运行标准的 benchmark 并与其他自动机加速器/处理器对比,我们细致地评估与分析了 LAP 的各项性能。第四章是本文的第二项核心工作,主要讲述了基于 LAP 核心和通用处理器的异构计算片上系统的设计、实现与评估。第五章将对本文的工作进行总结,并展望未来可开展的工作。

#### 第2章 基础理论与部署平台

本章将首先介绍自动机的基础理论和相关学术研究,最后重点阐释 ADFA 模型(第3章中介绍的自动机处理器 LAP 所使用的计算模型)。同时,本章将介绍 ZYNQ 系列 FPGA 的基础架构和特征。通过了解 ZYNQ,读者将可以更好地理解本文是如何依托现有硬件框架构建的 LAP SoC 片上系统(见第4章)。

#### 2.1 自动机理论与各类自动机模型

有限自动机<sup>[13]</sup>(finite automaton, FA),又称有限状态机(finite-state machine, FSM),是表示有限个状态以及在这些状态间进行转移和动作等行为的数学计算模型。同时,有限自动机也是非常有效的可用于进行模式匹配的算法工具。我们可以把数以千计的正则表达式编译成单个自动机,然后将我们需要处理的字符流输入该自动机进行模式匹配计算。通过这样的方式,我们可以同时匹配大量的模式而不是每次只匹配一个模式。自动机处理器正是基于这些数学模型所设计的。因此,本节将介绍两类基本的自动机模型及其衍生模型。

#### 2.1.1 DFA 与 NFA 模型

确定性有限状态机(Deterministic Finite Automata, DFA)和非确定性有限状态机 (Non-deterministic Finite Automata,NFA) 是最经典的两类自动机模型。

非确定性有限自动机 (NFA) 可表示为一个五元组 ( $Q, \Sigma, \delta, q0, F$ ):

- 有限的状态集合 Q;

- 有限的输入字符集合  $\Sigma$ ;

- 状态转换函数 δ(q,α);

- 自动机的初始状态 q0 ( $q0 \in Q$ );

- 接受态状态集合  $F(F \subset Q)$ 。

其中,状态转换函数  $\delta(q,\alpha)$  定义了当前状态 q 在接受输入字符  $\alpha$  后会激活的一组状态集合。这意味着,单个初始状态可能会接受一个输入字符而激活多个目标状态。更进一步的,这些目标状态又可能在接受同一个输入后各自激活更多的状态。因此,NFA 模型中,同一时间可能有多个活跃状态。

确定性有限自动机 (DFA) 是 NFA 的特例,由类似五元组 ( $Q, \Sigma, A, q0, F$ ) 构成。

- 有限的状态集合 O;

- 有限的输入字符集合  $\Sigma$ :

- 状态转换函数 Δ(q,α);

- 自动机的初始状态 q0 ( $q0 \in Q$ );

- 接受态状态集合  $F(F \subset Q)$ 。

不同之处在于,DFA 模型的状态转换函数  $\Delta(q,\alpha)$  每次只会激活一个状态,而不会激活一组状态集合。DFA 起初只有一个活跃的初始状态,每次该状态只会激活另一个状态。因此,DFA 模型在执行过程中,只会同时有一个活跃状态。

每一个 NFA 模型都可以转化为等价的 DFA 模型。但是如表格2.1所示,DFA 和 NFA 模型在时间复杂度和空间复杂度之间各自做了极端的权衡,因此各有利弊。NFA 模型有着有限的体积,不过对于每个输入字符需要进行更多的操作;等价 DFA 模型的计算操作得到了简化,却需要占用更多的存储空间。

| 状态机类型           | 计算复杂度        | 存储复杂度         |

|-----------------|--------------|---------------|

| 非确定性有限状态机 (NFA) | $O(n^2)$     | O(n)          |

| 确定性有限状态机 (DFA)  | <i>O</i> (1) | $O(\Sigma^n)$ |

表 2.1 有 n 个状态的 NFA 和等价 DFA 的存储复杂度和计算复杂度对比

#### 2.1.2 正则表达式到 NFA 的转化

正则表达式是计算机科学的一个概念。它使用单个字符串来描述、匹配一系列匹配某个句法规则的字符串。在很多文本编辑器里,正则表达式就通常被用来检索和替代匹配某个模式的文本。不仅如此,正则表达式被广泛的应用在各种模式匹配的应用中,比如深度网络包检测和非结构化数据挖掘。接下来我们将展示一个关键的过程:我们是如何将正则表达式集合转化为单个自动机模型的。此处,我们主要展示转化为NFA和DFA的过程。在后面的章节,我们会进一步展示正则表达式向其他衍生模型的转化。

为了讨论方便,自动机模型可以通过带标签的有向图来直观的表示。因此,此处将使用这一表示方法来形象的表示具体的 DFA 和 NFA 模型。具体来说,有向图的一个节点对应自动机中的一个状态。同时,每条边代表两个状态间的转换关系。每条边上的标签代表了转换触发所需要的条件,也就是当前输入字符应该满足的条件。通常来说,非接受态的状态使用单个圆圈表示,而接受态状态使用同心双圆圈表示。

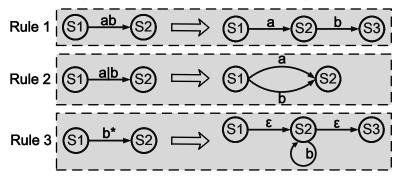

正则表达式可以很自然地转化为 NFA 模型。图2.1展示了将正则表达式转化为对应的 NFA 的三条规则。

- 规则 1: 如果待匹配的正则表达式子串是连续的字符,这表示我们想按顺序不间断的匹配这些字符。这意味着,我们可以将这些字符拆解为多次状态转换,并将这些过程顺序地连接起来。

- 规则 2: 如果待匹配的正则表达式两个子串间是"或者"(符号表示为 |) 的

关系,我们可以将这两部分拆解成拥有同一源头和同一目标的两个"并联的"转换过程。

• 规则 3: 如果待匹配的正则表达式子串是包含在克莱尼(Kleene, 符号表示为 \*)星号里的,这表示该子串可以出现 0 次或者无数次。这样的子串应该转化为如图2.1最下方所示的结构。(该子串两端引入了  $\epsilon$  边。)

图 2.1 正则表达式转化为 NFA 的三条规则

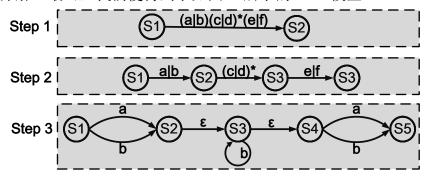

如图2.2所示,我们可以利用上述三条规则,将正则表达式 (a|b)(c|d)\*(e|f) 转化为对应的 NFA 模型。第一步,我们将该正则表达式拆解为串行连接的三个子串部分,并按照规则 1 进行分解。第二步,我们使用规则 2 和规则 3 将 "|"和"\*"进行分解。最终,我们便得到了如图2.2所示的 NFA 模型。

图 2.2 示例: 正则表达式转化为 NFA

#### 2.1.3 NFA 模型到 DFA 模型的的转化

如果需要进一步得到 DFA 模型,我们可以首先将正则表达式转化为 NFA 模型,再将该 NFA 模型转化为对应的 DFA 模型。在将 NFA 转化为 DFA 的过程中,我们需要使用子集构造法。**子集构造法**<sup>[29]</sup> 可以将输入的 NFA 模型转化为对应的 DFA 模型。利用该算法生成的 DFA 模型有这样一个特点:输出 DFA 模型中每一个状态对应着输入 NFA 模型的一个状态集合。更具体来说,子集构造法构造的 DFA 在接受输入序列  $a_1,a_2,a_3,...,a_n$  之后,能到达的状态应当对应于输入 NFA 模型的一个状态集合。该状态的集合包含着输入 NFA 模型沿着  $a_1,a_2,a_3,...,a_n$  序列

将会激活的所有状态的集合。

在完整介绍子集构造算法前,我们先定义三个函数和两个变量。其中, s 表示 NFA 的单个状态, 而 T 表示 NFA 的一个状态集合。

- $\epsilon$  closure(s): 该函数定义从 NFA 模型的状态 s 开始,只通过  $\epsilon$  边能够到达的 NFA 状态的集合(状态 s 的  $\epsilon$  状态闭包);

- $\epsilon$  closure(T): 该函数定义从 T 中某个 NFA 状态 s 开始,只通过  $\epsilon$  边能够 到达的 NFA 状态的集合( $\cup_{s\in T}\epsilon$  closure(s));

- move(T, a): 该函数定义从 T 中的某个状态 s 出发,通过标号 a 的路径能够到达的 NFA 状态的集合。

- Dstates 是要我们要构建的 DFA 模型的状态集合;类似的,每个 Dstate 就是该 DFA 模型的一个状态。值得注意的是,每个 Dstate 对应着输入的 NFA 模型的一个状态集合。

- Dtran[T,a] 表示输出 DFA 中,状态 T (T 是一个 Dstate) 在接收到字符 a 后 会跳转到的 Dstate。

子集构造算法的伪代码如算法2.1所示。算法2.1的第一行中, $s_0$  是 NFA 的 开始状态。在读入第一个输入字符之前,输入 NFA 模型能够到达的状态集合 是  $\epsilon$  —  $closure(s_0)$ 。因此,Dstate 以该值初始化。随后,我们观察第二行开始的 while 循环。当不再有新的状态集合可以被构建出来,该 while 循环结束。每个 NFA 所对应的 DFA 模型,其状态一定是有限的。因此,该 while 循环一定会结束。在第三行代码中,对于需要处理(也就是未加标记)的 Dstate,我们要先给他加上标记,用来代表该状态已经被处理过了。随后,我们进入第四行的 for 循环。对于每一个可能的输入字符 a,我们获取 Dstate T 可以到达的状态闭包 ( $\epsilon$  — closure(move(T,a)))。对于每一个输入字符 a,我们都可能会构造出一个新的状态集合 U。第 6-8 行代码表明,如果 U 不在 Dstates 中(也就说这是一个新的状态集合),我们需要把 U 加入到 Dstates 中,用于被以后的 while 循环处理。如果 U 在 Dstate 中,说明这个状态集合我们已经探索和处理过了,无需重复构造。第 9 行代码意味着,我们将在 DFA 模型的状态转换表中添加一个新的项: DFA 状态 T 在输入字符为 a 时跳转到 DFA 的另一个状态 U。最终,我们获得了要构建的 DFA 模型的状态集合 Dstates 和其状态转换表 Dtran。

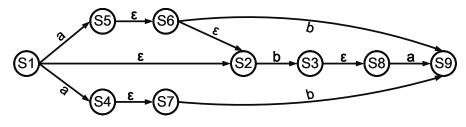

图2.3中展示了一个示例 NFA 模型, 我们将使用子集构建算法构造其对应的 DFA 模型。其构造过程如下:

- 输入 NFA 模型的初始状态为 1,因此我们将 Dstates 初始化为  $\epsilon$  closure(1),也就是状态 1 的  $\epsilon$  状态闭包 {1,2}。

- 随后进入 while 循环,我们处理 Dstates 中唯一一个未被标记的状态 T={1,2}, 并给这个状态加上标记。

#### 算法 2.1 子集构造法: NFA 模型转化成 DFA 模型

Data: 输入的 NFA 模型

Result: 要构造的 DFA 模型的状态集合 Dstates 和其状态转换表 Dtran

- 1 初始化时, $\epsilon$  *closure*( $s_0$ ) 是 Dstate 中的唯一状态,而且该状态未被标记;

- 2 while 在 Dstates 中存在一个未标记的状态 T do

- 进入 for 循环,对于输入字符 a,我们得到的新的  $\epsilon$  状态闭包  $U = \epsilon closure(move(T,a))$ ,也就是 {2,4,5,6,7}。新构建的状态 U 不属于 Dstates。因此,我们将 U={2,4,5,6,7} 不加标记的加入 Dstates 中,同时在 DFA 状态转换表中增加一项 Dtran[{1,2},a] = {2,4,5,6,7}。

- 随后,进入 for 循环的第二个循环,并处理输入字符 b。我们得到一个新的  $\epsilon$  状态闭包, $U = \epsilon closure(move(T,b))$ ,也就是 {3,8};状态 U 不属于 Dstates。因此,我们将 U 不加标记的加入 Dstates 中,同时在 DFA 的状态 转换表中增加一项 Dtran[{1,2},b] = {3,8}。

- 回到外层 while 循环, 此时 Dstate 中有两个未标记状态 {2,4,5,6,7} 和 {3,8}。

- 后续循环同理可得......

图 2.3 需要被转化为 DFA 的 NFA 模型

最终,我们获得了要构建的 DFA 模型的状态集合和其状态转换表(如表格2.2所示)。**状态转换表**在后面的章节还会用到,我们在此处稍加解释。如表格2.2所示,表格第一列列举了 DFA 模型中全部的状态,而第二、第三列则分别表示每个 DFA 状态在接受不同输入字符时会转换到的目标状态。如果输入字符集合  $\Sigma$  不是  $\{a,b\}$ ,那么表格的列数和列标题将做相应的调整。值得注意的是,NFA模型也可以用状态转换表表示。在 NFA 模型的状态转换表中,每个状态的目标

状态不再是一个状态,而可能是一个状态集合。

| DFA 状态 \输入字符 | a           | b       |

|--------------|-------------|---------|

| {1,2}        | {2,4,5,6,7} | {3,8}   |

| {2,4,5,6,7}  | {}          | {3,8,9} |

| {3,8}        | {9}         | {}      |

| {3,8,9}      | {9}         | {}      |

| {9}          | {}          | {}      |

表 2.2 子集构建法生成的 DFA 模型状态转换表

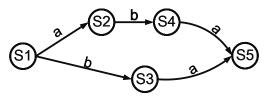

表格2.2对应的确定性有限状态机模型如图2.4所示。在新生成的 DFA 模型中,我们对每个状态进行了重新的编号: NFA 中的状态集合 {1,2} 对应 DFA 中的状态 1; NFA 中的状态集合 {2,4,5,6,7} 对应 DFA 中的状态 2; NFA 中的状态集合 {3,8} 对应 DFA 中的状态 3; NFA 中的状态集合 {3,8,9} 对应 DFA 中的状态 4; NFA 中的状态集合 {9} 对应 DFA 中的状态 5。

图 2.4 子集构建法生成的 DFA 模型

#### 2.1.4 Delayed Input DFA 模型

#### 1. $D^2FA$ 模型简介

Delayed Input DFA ( $D^2FA$ )<sup>[30]</sup> 是一种衍生 DFA 模型。 $D^2FA$  模型同样可以用 DFA 的五元组 ( $\mathbf{Q}, \boldsymbol{\Sigma}, \boldsymbol{\Delta}, \mathbf{q0}, \mathbf{F}$ ) 来描述。不同之处在于, $D^2FA$  的状态转移函数  $\Delta$  在接受一个输入字符后,所需要进行的操作更为复杂。DFA 模型在进行状态跳转时,只需要查询当前状态的跳转表,并根据输入字符从表中选择一项,即可得知跳转的目标状态(Next State)。 $D^2FA$  模型对每个状态的状态转移表进行了"增量式"的存储。因此, $D^2FA$  模型的状态转移函数需要连续对一到多个状态的转移表进行查询,才可以确定跳转的目标状态。在进行连续访存的过程中,当前输入字符被 delay(延迟处理)了;直到该过程结束,当前输入字符才被真正地被  $D^2FA$  模型消耗掉。因此,我们称之为 Delayed Input DFA。在存储同样的正则表达式时, $D^2FA$  模型相比于传统的 DFA 模型可以减少 95% 的存储开销。

$D^2FA$ 模型的初衷是为了实现存储更紧致的 DFA 模型,也就是说用更少的存储空间存储相同功能的 DFA。对于任何的正则表达式集合,都存在一个拥有最少状态的 DFA 模型与之对应。然而,传统的 DFA 模型需要非常大的存储空间,

用于存储其状态间的跳转关系。最坏情况下,用来表示这个 DFA 模型所需要的存储器容量为: DFA 状态数和每个状态的出边上限数的乘积。如果输入字符使用 ASCII 码编码,那么每个状态最多有 256 条出边;同时,用于网络入侵检测的正则表达式集合通常包含上百条模式。对应的,该 DFA 模型将包含上千个状态,并需要几百兆的存储空间。更不利的是,每个状态的跳转表自身很难用一般的压缩技术进行压缩。这是因为,每个状态在不同输入下都有着不一样的目标状态。因此,在每个状态内部,这些边无法被有效压缩。

$D^2FA$ 模型的状态转移函数比 DFA 模型的转移函数更复杂: 其状态转移函数支持  $D^2FA$  模型中引入的新类型的边——"默认边" (Default Edge)。虽然对于每个 DFA 状态,它的 256 条出边我们很难去压缩。但是,基于 DFA 模型中状态之间的相似性, $D^2FA$  提出了新的压缩思路。假设 DFA 模型中有两个状态  $s_1$  和  $s_2$ ,并且它们接受相同的输入字符  $c \in C$  时,都会跳转到同一个目标状态  $s \in S$ 。我们称之为: 状态间的相似性。利用该相似性,我们可以消除  $s_1$  中的这些出边,并用一条从  $s_1$  指向  $s_2$  的 Default Edge 来替代它们。通过这种方式,  $s_1$  中的边将仅仅包含和  $s_2$  中行为不一样(接受相同输入字符,目标状态不同)的边。

图2.5左半边展示了一个示例 DFA 模型。该 DFA 接受三个模式: a+,b+c 和 c\*d+(\*\*表示匹配 0 或者无穷个\*前方的字符,+表示匹配 1 或者无穷个+前方的字符),且其输入字符集合为 {a,b,c,d}。该 DFA 的初始状态(inital state)是状态 1,而状态 2,4,5 则是其接受态(对应于要匹配的三个模式)。图2.5的右半边展示了对应的  $D^2FA$  模型。其中,没有标签的边指代  $D^2FA$  模型中引入的 Default Edge。在处理当前输入字符时,如果当前状态没有针对该字符的有效边,default edge 就会被用来确定下一个状态。假设当前输入字符流是 aabdbc,那么左边的自动机会依次访问状态 1223435,而右边的自动机会依次访问状态 1212314135。此处,有下划线的状态代表该自动机中的接受状态。可以看到,DFA 和对应的 $D^2FA$  在接受相同的输入字符流后会进入的接收状态。也就是说,这两个自动机的匹配结果是一致的。事实上,我们可以证明这两个自动机的功能完全等价。

图 2.5 DFA 和  $D^2FA$  模型,接受三个模式: a+,b+c 和 c\*d+

从图2.5中可以发现,DFA 模型有 20 条边,而其对应的  $D^2FA$  模型只有 9 条边。在实际的应用中,DFA 的规模要大的多,使用  $D^2FA$  模型进行压缩的收益可以提升到 95%。然而, $D^2FA$  模型也是有缺点的。我们可以注意到,在 Default Edge 被触发时,当前输入字符不会被处理掉,而是会被"Delay"(延迟处理)。因此,这样的压缩方式会使得  $D^2FA$  的字符处理速度比对应的 DFA 模型慢。

#### 2. 构建 $D^2FA$ 模型的基本原理

我们没有通用的算法直接生成一个  $D^2FA$  模型。事实上,我们需要基于已有的 DFA 模型,构建其对应的  $D^2FA$  模型。具体来说,我们在需要在原本的 DFA 模型上,系统地使用 default edge 替换原本的边。在这个过程中,DFA 模型 和  $D^2FA$  模型的等价性必须一直被保持。

定理 1: 在  $D^2FA$  模型中,如果两个不同的状态 u 和 v 满足以下条件,我们就可以引进一条从 u 指向 v 的 default edge,同时去掉 u 中从 u 到 delta(a,u) 的边。我们可以证明,这个过程前后,该  $D^2FA$  模型是等价的。具体条件如下:

- u 有一条标签为字符 a 的出边;

- u 没有向外的 default edge;

- $\delta(a, u) = \delta(a, v)$ .

基于定理 I,我们可以得到更进一步的结论。如果存在多个输入字符 a 满足  $\delta(a,u)=\delta(a,v)$ ,那么在 u 和 v 之间引入  $default\ edge\$ 将可以消除多条边。构建  $D^2FA$  的过程,就是在原本的 DFA 上不断使用定理 I 进行边的替换。由于每一步 都维持了模型的等价性,最初的 DFA 模型和最终得到的  $D^2FA$  模型是等价的。图2.5右边的  $D^2FA$  模型就是在图左边 DFA 模型的基础上,依次在以下节点间增加  $default\ edge\$ 构建出来的:(2,1),(3,1),(5,1) 和 (4,1)。

#### 3. 如何构建边最少的 $D^2FA$ 模型

对于每个状态,只能有一条向外的 default edge。因此,我们需要很仔细的选择每个状态的默认状态,从而最大化冗余边的消除。同时,有一点需要一直被满足:不能形成由默认边组成的环。在这样的限制下,默认边将共同组成树形结构。并且,这些边将成为指向树的根节点的有向边。因此,我们可以把选择默认边集合的过程转化为带权重的最大生成树问题。同时,我们把每个 DFA 用来产生  $D^2FA$  生成树的图称为 space reduction graph(空间缩小图)。对于任何一个给定的 DFA 模型来说,它的空间缩小图是一个无向的完全图,而且拥有和原本的 DFA 完全一样的顶点集合。空间缩小图中,任意两个节点间会被赋予一个权值w(u,v)。其中,w(u,v) 的值是节点 u 和节点 v 间满足  $\delta(a,u) = \delta(a,v)$  的边的数目总和减去 1。如果 u 和 v 之间没有任何这样的边,那么 u 和 v 之间则不存在边。图2.5左边 DFA 对应的空间缩小图如图2.6所示。可以看到2.5右边的  $D^2FA$  模型的默认边组成了一棵生成树。而且,这棵树正是从图2.6中选择的。该生成树边

的权重总和为 3+3+3+2=11,这也正是图2.5中的 DFA 模型和  $D^2FA$  模型的边的总数的差。

图 2.6 接受 a+,b+c 和 c\*d+ 的 DFA 的空间缩减图

#### 4. 约束默认路径的最大长度

值得注意的是,从空间缩小图中选择不同的生成树就会生成不同的  $D^2FA$  模型。而且,空间缩小图往往有着多棵最大生成树。如图2.7所示,图2.6可以有着两种不同结构的最大权重生成树。这两棵树边的总权重是一样的,这意味着对应的  $D^2FA$  模型的边的总数是一样的。但是,我们还需要考虑他们的**最大默认路径** (由默认边组成的最长路径)。例如,图2.7左边的最大默认路径为 3,而右图的最大默认路径为 2。当自动机沿着默认路径进行状态切换时,是不会处理任何输入字符的。因此,最大默认路径越大, $D^2FA$  模型的最坏情况下的字符处理速度就越低。

图 2.7 空间缩减图可生成的不同的最大权重生成树

如果我们的目标仅仅是最小化  $D^2FA$  模型的存储空间,那么我们只需要在空间缩减图中运行最大生成树的搜索算法即可。事实上,我们还需要解决另一个问题:每条默认边的方向如何选择。我们可以随机的在树中选择几个根节点 (root),并让所有默认边都指向根节点的方向。但是,该方法构造的生成树往往会有很长的最大默认路径。这意味着,对应的  $D^2FA$  模型需要经过很多次默认

切换(default transition)才能处理掉一个输入字符。 $D^2FA^{[30]}$  中采用的办法是:在构造最大生成树时,保证树的直径不会大于一个固定的阈值,从而约束整棵树的最大默认路径。

采用上述方法构建最大生成树的过程分为两步。

- 基于 Kruskal 算法<sup>[31]</sup>,按照空间缩减图中边权重 d 的降序依次检验每条边,对于每条被检验的边 u,v:

- 如果他不属于同一棵树,而且增加这条边也不会创建一棵直径超过固 定阈值的树,则这条边可以被选择;

- 否则,继续检验下一条边。

- 一旦所有的边都被检验过了,我们就会得到一棵或者多棵生成树。其中,树上的边就是我们要添加在  $D^2FA$  模型中的默认边。

- 我们为每棵生成树选择一个根节点,使得其叶子结点到根节点最短路径的 长度总和最小。值得一提的是, 检测树的直径是一个比较复杂的计算过程。 此处我们不展示该算法的伪代码, 我们将在下一节给出其优化版本的伪代码。

### 2.1.5 ADFA 模型

相比 DFA 模型,Delayed Input DFA( $D^2FA$ )模型实现了非常紧致的存储。但是, $D^2FA$  模型却有着两点明显的不足。第一, $D^2FA$  模型缺少最坏情况下执行时间的保障,坏的输入序列可能会使其频繁触发默认边从,从而极大的降低字符处理速度;第二,该构建过程的计算复杂度很高。为了解决  $D^2FA$  模型中存在的两个问题,M. Becchi 等人提出了相应的优化。

#### 1. ADFA 模型简介

**ADFA**<sup>[32]</sup> (Amortized time/bandwidth overhead DFA) 模型是  $D^2FA$  模型的优化版本。它可以直接用  $D^2FA$  (见第1小节) 的五元组 (Q, $\Sigma$ , $\Delta$ ,q0,F) 来描述。 ADFA 模型与  $D^2FA$  模型在数学上的表示和实际执行时的操作完全一致。两者唯一的不同在于,他们的构建过程和构建完成后状态间的连接关系不同。具体来说,ADFA 模型与  $D^2FA$  模型都是用"Default Edge"来替代 DFA 模型中的一些冗余边;然而,ADFA 模型在选择"Default Edge"时和  $D^2FA$  模型采取了不一样的算法。因此,构建  $D^2FA$  模型和 ADFA 模型所需要的算法复杂度是不同的。更重要的是, $D^2FA$  模型和 ADFA 模型最终需要的存储空间和运行时的访存次数是不同的。

相比于  $D^2FA$  模型,ADFA 模型有着两个显著的优势。

ADFA 模型可以保证,对于任意长度为 N 的输入字符流,ADFA 模型最多产生 N(k+1)/k 次状态转换(包括沿着普通边和沿着默认边进行状态转换)。

因此,ADFA 模型可以提供最坏情况下执行时间的保障。此处,k是一个正

整数。随着 k 值的增大,ADFA 模型的状态转换次数将逐渐接近 DFA 模型。同时,ADFA 模型的性能也会不断接近 DFA 模型。不过与此同时,ADFA 模型的压缩效果也会不断下降。特别的,k=1 时 ADFA 模型可以取得最大化的压缩效果。此时,ADFA 模型可以保证:最坏情况下,处理长度为 N的输入字符流只需要 2N 次状态转换。相对应的, $D^2FA$  模型的最坏情况状态转换次数则是取决于其生成树的最大默认路径(往往远大于 2)。总的来说,ADFA 模型可以让用户灵活的地在存储和执行速度之间做权衡。通过详细的评估可以发现:

- 在实现相同程度的压缩效果时,ADFA模型可以提供比 $D^2FA$ 更好的执行速度:

- 在提供相同的最坏执行速度保证时,ADFA 模型可以取得 10 倍于  $D^2FA$  模型的压缩效果。

- 在基于正则表达式集合构造对应的 ADFA 模型时,我们不需要先构造出对应的 DFA 模型,而是可以根据 NFA 模型直接构造出对应的 ADFA 模型。这是因为,ADFA 的构造算法可以嵌入在 NFA 到 DFA 的转换算法 (即算法2.1) 之中。在构建 ADFA 模型之前,我们不需要先构造出一个可能规模大到不可行的 DFA 模型。这使得 ADFA 模型可以支持更大规模的正则表达式输入。而且在构造 ADFA 模型时,我们不需要维护一个规模非常大的图结构。总的来说,ADFA 模型的构造算法的时间、空间复杂度相比  $D^2FA$ 的构造算法要低得多。

# 2. ADFA 模型的核心思想

ADFA 模型的提出基于如下观察: 正则表达式匹配的计算过程都开始于单个初始状态 (initial state); 自动机中存在大量"往回指的边",它们要么指向自动机的初始状态,要么指向在抵达当前状态之前途径过的一些邻居。事实上,在 $D^2FA$ 模型中,被压缩的边主要就是这些"往回指的边"。

定义 1: 自动机中的每个状态都有一个固定的属性:state depth(状态深度)。 每个状态的状态深度是一个非负整数,等于在状态转移图中该状态到自动机初始 状态的最短距离。

也就是说,自动机初始状态  $s_0$  的深度为 0;  $s_0$  可以直接到达的一组状态  $S_1$  的深度都是 1;  $S_1$  中的状态可以直接到达的另一组状态  $S_2$  的深度都是 2; 以此类推。借助于这个概念,我们可以有如下两条定理:

定理 2: 在 DFA 中,如果任何一条默认边都满足: 其出发状态的深度  $d_i$  大于它的目标状态的深度  $d_j$ ,那么处理任何输入到该自动机的长度为 N 的字符流所需要的状态切换总数(包括沿着默认边的切换)不会超过 2N。换句话说,一个只有回向默认边的 DFA 可以保证: 最多需要 2N 的时间进行长度为 N 的字符流处

理。

定理 2 的证明过程如下。对于 ADFA 模型,每一个输入字符会导致恰好一次常规状态转换(labeled transition)和零或多次默认转换(default transition)。设想某个时间节点,一连串 d 个默认转换将从状态 s 开始被触发。根据定理 2 的假设,我们知道默认转换总是朝着深度更浅的状态。因此,状态 s 的深度一定是大于等于 d。也就是说,在此之前至少有 d 次常规转换发生了。因此,默认转换的次数总是至少比常规转换的次数小 1。不仅如此,长度为 N 的输入字符流只会引发 N 次常规转换。因此,该过程中总的状态转换数不会大于 2N-1。

定理 3: 在 DFA 中,如果任何一条默认边都满足: 其出发状态的深度  $d_i$  和其目标状态的深度  $d_j$  满足:  $d_j \leq d_j - k(k)$  是任意正整数)。那么,处理任何输入到该自动机的长度为 N 的字符流所需要的状态切换总数(包括沿着默认边的切换)不会超过 N(k+1)/k。

定理 3 是定理 2 的推广。定理 3 中,默认边的出发状态和目标状态的深度差不再要求是大于等于 1,而是进一步要求大于等于 k。定理 3 的证明如下。最坏情况下,在发生最少数量的常规转换后就会发生一次默认转换。而默认转换的始终状态的深度的差值大于等于 k,因此在发生每次默认转换前至少要发生 k 次常规转换。也就是说,最坏情况下,每 k 次常规转换后发生一次默认转换。这意味着,为了处理长度为 k 的输入字符流,最多发生 k+1 次状态转换。也就是说,长度为 N 的输入字符流最多需要 N(k+1)/k 次状态转换。

#### 3. ADFA 模型的构建算法

ADFA 模型构建算法的目标是为了实现一个有 default transition(默认转换)的 DFA。而且该 DFA 应当可以实现最大程度的模型压缩,并保障最坏情况下的 状态转换开销。基于定理 2 和定理 3,我们可以利用有向图上最大生成树问题来形式化地描述 ADFA 的构建过程。同  $D^2FA$  一样,我们也把这样的有向图称之为 space reduction graph(空间缩减图)。

ADFA 模型的空间缩减图可按以下四步构建:

- 为 DFA 模型中的每一个状态在 ADFA 的空间缩减图中创建一个副本;

- 对于空间缩减图中的每一个点对,如果点  $s_1$  的深度和点  $s_2$  的深度差不小于 k,在  $s_1$  和  $s_2$  之间添加一条边;

- 为第二步中添加的边设置方向(从深度更深的指向深度更浅的);

- $n_X$  和  $n_Y$  之间边的权值等于  $s_X$  和  $s_Y$  之间有着相同行为的边的总数。其中,  $s_X$  和  $s_Y$  是 DFA 中的两个状态,而  $n_X$  和  $n_Y$  是状态缩减图中对应的两个点, 在空间缩减图中,每一条边意味着一条可以被选择的默认边(default edge)。 同时,这些边的权重代表着: 如果这条默认边被选用,可以移除多少带标签的常规边。每个 DFA 状态最多只能有一条向外的默认边。因此,挑选一组最佳的默

认边(实现最大程度的模型压缩)等价于在这个有向图中搜索一个最大生成树(或者森林)。不同于  $D^2FA$  模型,ADFA 模型在找到最大生成树(或者森林)后无需再计算每条边的方向,也无需确定根节点。这是因为,ADFA 的空间缩减图是有向图。另一点不同于  $D^2FA$  的地方是,ADFA 在搜索最大生成树时,不需要化解可能在图中产生的环状结构。这是因为,ADFA 的状态缩减图从一开始就不包含任何环:每条边都是从深度更深的节点指向深度更浅的节点,因此不会产生环状结构。因此,ADFA 模型在构建时可以省掉这一计算复杂的过程。

ADFA 模型中引入空间缩减图的概念是为了和  $D^2FA$  的算法做对比。事实上,我们在构建 ADFA 模型的最大生成树时,不需要构建这样一个庞大的图结构作为辅助。具体来说,这个图问题可以降维成:每个 DFA 状态,从比自己深度浅(深度差大于等于 k)的节点中,找一个和自己有着最多相同行为的边的节点作为自己的默认状态。当有多个节点满足条件时,优先选择深度最小的节点。(这样可以减少最大默认路径,同时优化访存的局部性。)

如果我们进行 DFA 模型的广度优先遍历,那么节点深度的计算和默认边的选择可以在一次遍历中做完(伪代码如算法2.2所示)。在该算法中,DFA 可以被描述为状态总数 n 和状态转移函数  $\delta(states, \Sigma) \rightarrow states$ 。当一个状态 s 从 queue 中被抽取出来时,所有深度比他小的节点都已经被处理过了。因此,这些节点的 depth 已经被赋予了一个正确的值。虽然比状态 s 深度更深的节点还未被处理,但是他们的深度都已经被初始化 n。因此,这些节点不会引发错误的操作。事实上,去除冗余边的操作也可以在这一次算法遍历中完成。类似的,该算法还可以和先前提到的子集构造法(算法2.1)组合在一起。因为在子集构造法中,DFA 状态节点正是按照与本算法相同的访问顺序被构造的。

# 2.1.6 其他的衍生自动机模型

除了  $D^2FA$  和 ADFA 模型外,还有很多衍生的自动机模型。这些衍生模型 通常为了解决以下两个目标中的一个:

- 通过压缩机制实现更小的 DFA 内存占用。该目标并不包括解决状态爆炸的问题。相反的,这一类自动机通常是为可行的 DFA 提供一个有效的紧致的存储方式。它们往往利用边的冗余性进行自动机模型的压缩。前文提到的  $D^2FA$  模型(1)和 ADFA 模型(2.1.5)就是属于这一类自动机模型。该类别的类似模型还有  $\delta$ FA [33] 模型。

- 在 DFA 模型变得不可行时(发生状态爆炸时),用来替代 DFA 模型。这一类自动机包括 XFA<sup>[34][35]</sup>、HistoryFA<sup>[36]</sup>、HybridFA<sup>[37]</sup>、MultipleDFA<sup>[38]</sup>和 BFSM<sup>[39]</sup>。值得一提的是,这些模型往往是基于 DFA 模型的拓展,它们需要借助于一个高效的 DFA 模型作为核心模块。

#### 算法 2.2 ADFA 构建算法

```

Data: DFA dfa=(n,\delta(states,\Sigma)); 整数 k

Result: 数组 default[n]

1 初始化空队列 queue 和初始化空数组 depth[n];

2 for state s \in states do

3

depth[s]=n;

default[s]=s;

5 end

6 depth[0]=0;

7 queue.push(0);

8 while !quque.empty() do

state s = queue.pop();

int saving=1;

10

for char c \in \Sigma do

11

if depth[\delta(s,c)] = n then

12

depth[\delta(s, c)] = depth[s] + 1;

13

queue.push(\delta(s, c));

end

15

end

16

for state t \in states \&\& depth[t] \le depth[s]-k do

17

int common=common transitions(s,t);

18

if common>saving || (common==saving && depth[t]<depth[default[s]]) then

19

default[s]=t;

20

saving=common;

21

end

22

end

23

24 end

```

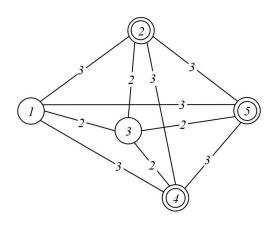

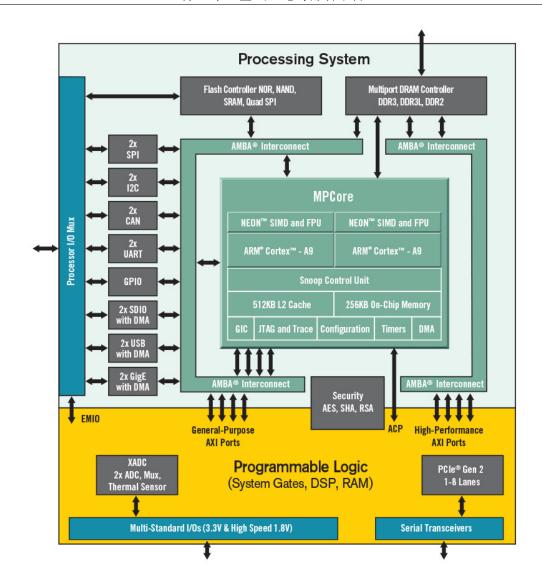

# 2.2 ZYNQ 的异构计算平台

ZYNQ-7000<sup>[40]</sup> 代表了一系列基于 Xilinx SoC 架构 FPGA 芯片。这些产品将拥有丰富特性的通用处理器系统(PS)和 28 纳米工艺的 Xilinx 可编程逻辑 (PL) 集成到了同一个芯片中。其通用处理器系统通常基于双核心或单核心 ARM Cortex-A9。不仅如此,该系统还包括片上存储器、外部 DDR 接口以及丰富的外设接口。通过这样的方式,ZYNQ 的单个芯片可以同时提供通用处理器的普适计算能力和 FPGA 的定制计算能力。

#### 2.2.1 CPU+FPGA 的架构

ZYNQ-7000 的架构框图如图2.8所示。图2.8上半部分是基于 ARM CPU 的通用处理系统,其核心是两枚最高主频达 1 GHz 的 Cortex-A9 处理器。除此以外,PS 部分还有丰富的外设控制器,包括以太网控制器、USB/SPI/I2C/CAN 等接口、UART 串行接口、8 通道 DMA 控制器、多功能 DRAM 控制器和 Flash 控制器。这些部件和 ARM CPU 通过 AMBA<sup>[41]</sup> 总线系统实现互联。

图2.8中黄色部分包括了现场可编程逻辑门阵列(FPGA)以及常用的逻辑硬核。可编程逻辑不同于 ASIC 电路,它是一种基于查找表的可编程电路。用户可以通过使用 Verilog 语言或者 VHDL 语言进行编程,设计他们想要的定制电路。然后,用户可通过 Vivado 集成开发工具,将 Verilog 代码编译成对应的逻辑结构和查找表。将生成的查找表写入 FPGA,就实现了对 FPGA 的烧写和逻辑定制。随着 FPGA 技术的发展,当代的 FPGA 逻辑中都包含了常用的硬核。这些硬核有着固定的内部逻辑和外部接口,灵活性要低于可编程逻辑。但是,他们往往拥有更高的能效、更快的速度和更低的面积占用。ZYNQ-7000的内置硬核资源包括:

- 36Kb 容量的块随机访问存储器 (BRAM), 最大支持 72bits 的宽度;

- 数字信号处理器 (DSP),可以支持 18 比特 \*25 比特的有符号乘法、48 比特的加法或者累加或者 25 比特的预加器;

- 可编程输入输出模块,可以支持 1.2V/3.3V 的 LVCMOS、LVDS 或 SSTL;

- 高速串行收发器,数据速率最高可达 12.5 Gb/s:

- 2代 PCIE 接口模块,最多支持 8 通道。

图2.8中 PS 部分和 PL 部分之间可以通过 EMIO GPIO 接口进行通讯。ARM 处理器可以通过该接口对 FPGA 进行引脚级的控制和读取。除此以外,PS 的 AMBA 总线系统也预留了 AXI 接口给 PL 部分。如图2.8所示,PS 可以通过标准的高性能 AXI 端口或者慢速的通用 AXI 接口对 PL 进行访问和控制。通过 AXI 接口的方式进行 PS+PL 的互联,可进行便捷的系统集成,也可以保证了通讯的速度和效率。因此,本文正是基于 AXI 总线进行的系统集成。

#### 2.2.2 AXI 总线系统

Xilinx 采用先进可拓展接口<sup>[42]</sup>(Advanced eXtensible Interface, AXI)协议进行知识产权核心(Intellectual Property, IP)的系统级集成。AXI 是 ARM 公司1996 年提出的 AMBA 总线协议的一部分,包含了一系列微控制器总线协议。第一个版本的 AXI 协议在 2003 年被提出。7 年后,AMBA 4.0 被提出。同时,AXI的第二个主要版本 AXI4 被提出。总的来说,一共有三种 AXI4 接口:

- AXI4: 面向高性能的内存映射式访问;

- AXI4-Lite: 低吞吐的内存映射式访问(比如对控制状态寄存器的访问)。

图 2.8 ZYNQ 体系结构总览

- AXI4-Stream: 面向高速的流数据的访问。

- Xilinx 产品广泛采用 AXI4 总线,获得了很高的生产率、灵活性和可用性。

- 由于只使用 AXI4 规范, IP 开发者只需要仅仅学习这一种协议。

- AXI4 提供 3 种上述协议,可以为不同的应用场景提供适用的协议。

- AXI4 是一种内存映射式接口,允许高吞吐的数据传输。AXI4 的单个地址发送阶段后可以附带最大 256 个数据周期的突发传输。

- AXI4-Lite 是一种轻量化的内存映射接口,不支持突发数据传输。它有很小的资源占用,而且是一个很小很简单的接口,便于开发者去实现和使用。

- AXI4-Stream 接口无需地址传输,而且可以有无限大小的突发数据传输。因此,AXI4-Stream 有着非常高的传输速率和简单的控制接口。

- 使用 AXI4 总线规范还极大地提高了产品的可用性。用户不仅仅可以使用

Xilinx 公司开发的 IP 核,还可以使用 ARM 社区提供的第三方 IP 核。

# 2.2.3 AXI4 直接内存访问

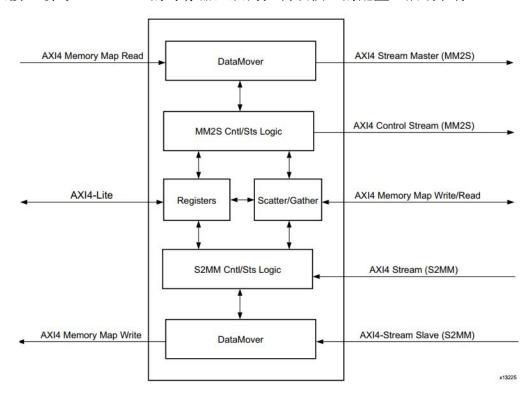

如图2.8所示,PS 和 PL 部分可以通过 AXI 总线进行数据传输。为了实现系统内存和 AXI4-Stream 类型的目标设备间的高吞吐数据传输,我们需要借助于 AXI4 DMA <sup>[43]</sup> 控制器进行高效的直接内存访问(Direct Memory Access,DMA)。Xilinx 公司提供的 AXI DMA 核心是一种软 IP 核。该 IP 不是固化在 Xilinx 的FPGA 中的硬件核心,而是需要用可编程逻辑搭建。AXI DMA 可以提供介于内存映射设备和 AXI4-Stream 接口设备之间的高带宽数据传输。它支持可以选的 scatter/gather 能力,可以代替中央处理器负责数据传输任务的控制和执行。图2.9展示了 AXI DMA 的功能组件。其中,最主要的数据搬运是通过两个内置的 DataMover 模块进行的。上方的 DataMover 可以从内存映射的设备(比如系统 DDR)中读取大量数据,并将数据写入到 AXI Stream 类型的目标设备中。而下方的 DataMover 则是从 AXI Stream 的设备中读取流数据,并将这些数据写入到内存映射设备中。这两个 DataMover 可以独立的工作。用户可以通过 AXI4-Lite 从接口读写 AXI DMA 的寄存器,从而控制该核心的配置、启动和停止。

图 2.9 AXI DMA 模块框图

# 第3章 LAP: 高效的轻量级自动机处理器核心

本文核心目标是实现更快的基于 ADFA 模型(见第2.1.5小节)的轻量级自动机处理器。一方面,ADFA 模型搭配上字母压缩策略实现了已知的最高效的 DFA 模型压缩<sup>[32]</sup>。尽管在编译复杂的正则表达式集合时可能会发生状态爆炸的问题,这使得 ADFA 模型不适用于所有场景下。但是,用来解决状态爆炸问题的有效方法<sup>[38][37][34][35][14]</sup> 却又往往使用 DFA 模型作为核心模块。因此,无论是否会发生状态爆炸,高效的 DFA 处理能力是必不可缺的。另一方面,本文提出的用于实现高效的 ADFA 执行的策略与解决状态爆炸问题的方法是完全正交的。因此,本文要解决的核心问题和提出的方案都是有着重要的意义的。

本章将主要介绍本论文的核心工作:轻量级的自动机处理器核心 LAP 的设计、实现与评估。(我们已经在国际会议上向国内外学者介绍过这一工作,对应的论文见第5.2小节。)我们将首先介绍 LAP 的研究动机。随后,我们将介绍 LAP 的硬件模型和 LAP 指令集。在第三节,我们将进一步拓展 LAP 的硬件模型,并优化 LAP 指令集。相应的,我们提出了两条新的硬件指令,它们将有助于实现更快的 ADFA 计算。在第四节,我们将阐释 LAP 的微体系结构,包括其流水线结构和细粒度多线程技术。第五节中,我们将讲述 LAP 编译器的实现。最后,我们将评估 LAP 的资源占用、性能和功耗。

# 3.1 研究动机

我们首先分析下已有的模式匹配专用硬件的不足。Micron 公司的 Automata Processor<sup>[15]</sup> 基于空间架构实现了高并发的基于 NFA 模型的执行,然而这样的架构需要基于大规模的 DRAM 存储器阵列,也需要复杂的硬件互联。另一方面,基于 DFA 模型的 RegX<sup>[14]</sup> 处理器需要借助于外部的大容量 DRAM 存储其自动机模型代码。为了掩盖 DRAM 访存延迟,它的内部还使用了较为复杂的层次化硬件 Cache。除此以外,HAWK<sup>[26]</sup> 和 HARE<sup>[25]</sup> 拥有非常复杂的硬件流水线。他们都有着共同的不足:需要借助于大容量的存储器而且拥有复杂且庞大的硬件架构。因此,这些专用硬件往往需要占用较大的芯片面积,同时产生较大的功耗。

我们试图设计并实现一款更轻量化的自动机处理核心,LAP。我们之所以称之为"轻量级"的处理器核心,是因为这款处理器满足两个特征:

• 在实现相同的模式匹配任务时,LAP 相比于已有的解决方案需要更小容量的存储器。这使得 LAP 可以将整个自动机模型存储进有限大小的 SRAM 中,并在不借助外部 DRAM 的情况下独立的运行。

• LAP 的硬件流水线所使用的硬件资源很少。在已有的 CPU 系统中添加 LAP 核心既不会显著提升芯片面积,也不会显著提高系统的总体功耗。

为了使得 LAP 的硬件流水线结构简单、资源占用少,我们选择了基于确定性有限自动机 (DFA) 模型实现模式匹配计算。非确定性有限自动机 (NFA) 有着非常高的计算复杂度。对于每一个输入字符,我们需要检查每一个 NFA 中活跃的状态,并实现这些状态的切换。因此,基于 NFA 模型的自动机专用硬件要么处理速度慢(串行进行状态切换),要么需要支持大规模的并行访存和计算。确定性有限自动机 (DFA) 最多只能有一个活跃状态。因此,对于每一个输入字符,DFA 只需要进行一次状态切换。事实上,在将 NFA 转化为 DFA 的过程中 (见算法2.1),我们已经充分挖掘了 NFA 中计算的冗余性并予以消除。总的来说,DFA 模型虽然相比 NFA 模型需要更大的存储空间,但是 DFA 模型极大地降低了所需要的计算量。而且随着很多优化技术被应用到 DFA 模型中,DFA 模型的存储需求也被极大地降低了。这使得 DFA 模型可以非常高效的执行在定制化的硬件体系结构上。

为了使 LAP 需要的硬件存储器容量大幅降低,我们需要高度压缩由正则表达式集合生成的自动机模型。真实的模式匹配任务(深度网络包检测、基因串匹配)往往需要同时匹配大量的正则表达式。因此,根据这些正则表达式产生的 DFA 模型往往也会体积较大。这使得我们需要消耗很多的片上资源用于存储模型的二进制代码。在 LAP 中,我们使用 ADFA 模型(一种优化后的 DFA 模型,详情见第2.1.5小节)代替 DFA 模型,作为主要的自动机模型。我们可以借助 ADFA 模型强大的压缩算法实现自动机模型的大幅压缩,从而降低存储器容量的占用。

尽管 UAP<sup>[27]</sup> 使用 ADFA 模型实现了较为轻量级的模式匹配计算,然而该处理器基于 ADFA 模型的处理速度却并不让人满意。ADFA 模型引进的 default transition(默认状态转换)可以实现高效的模型压缩,但同时也带来了更复杂的计算流程。这使得 UAP 在基于 ADFA 模型进行模式匹配计算时字符处理速度较慢。为了享受 default transition 带来的存储效益,又不过度损害自动机的处理速度,我们需要提出新的自动机执行算法。同时,为了支持新的执行算法,我们需要有新的硬件支持。本文正是按照这样的思路,采取软硬件协同优化的方式来设计和实现 LAP。相比于其他轻量级的自动机处理专用硬件,LAP 可以实现更快的处理速度。总的来说,我们的目标是实现一款更高效的轻量级自动机处理器。

# 3.2 LAP 的指令集设计

本文所设计实现的轻量级自动机处理器 LAP 不同于传统的冯诺依曼结构,它使用一种专门为执行自动机模型所设计的硬件抽象。同时,LAP 是一类可编程处理器,它拥有自己的指令集。本小节将先介绍 LAP 的硬件抽象模型,然后介绍其指令集。

# 3.2.1 LAP 的硬件执行模型

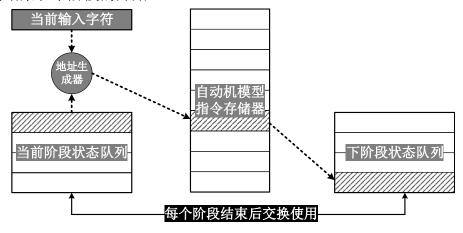

图3.1展示的是 LAP 所的硬件执行模型。该执行模型与 UAP<sup>[27]</sup> 和 UDP<sup>[28][44]</sup> 系统的执行模型类似,可以支持多种多样的自动机模型,包括 NFA、DFA、ADFA 以及其他已知的所有自动机模型。该硬件模型的功能是顺序处理一个包含 N 个输入字符的字符流。此处,我们把该自动机处理器硬件模型的执行过程划分成相邻的 N 阶段。每当处理完字符流中的一个字符后,该自动机处理器会紧接着读取该字符的后一个相邻字符。同时,当前输入字符被处理和消耗掉,意味着当前阶段的结束和下阶段的开始。

图 3.1 LAP 的硬件执行模型

"当前阶段状态队列"是使用寄存器组实现的硬件队列(Queue),存储当前阶段被激活的所有自动机状态。之所以使用队列,是为了支持非确定性有限自动机:非确定性有限自动机可能有多个状态同时处于活跃状态。如果不需要支持 NFA 模型,那么该执行模型中的两个队列可以换成单个寄存器。每个执行阶段,我们需要按顺序从当前阶段状态队列中依次取出所有的活跃状态,并顺序的处理他们的状态切换。最简单的情况下,对于取出的每一个活跃状态,LAP 架构将根据取出的当前状态和当前输入字符计算出相应的指令地址。然后,LAP 从自动机模型指令存储器中取出一条指令。该条指令编码了当前状态在接受当前输入的情况下应该切换到的目标状态。于是,我们将该目标状态写回"下阶段状态队列"。等到"当前状态队列"为空时,也就是说所有的活跃状态都处理完后,

LAP 将交换"当前状态队列"与"下阶段状态队列"。通过这样的方式,在处理 完当前输入字符后,"当前阶段队列"会包含所有上个阶段被激活的自动机状态, 而"下阶段状态队列"又会变成空队列。如此便可以循环往复。

值得一提的是,为了支持各种各样的自动机模型,从"当前状态队列"中取出的每个状态的处理过程并不总是像上述过程那么直接和简单。在 LAP 中,每一个自动机状态拥有特定的一种类型。上述过程讲述的恰好是最简单的一类自动机状态: BASIC 类型。对于有着复杂类型的自动机状态,在处理这一个状态的切换时,LAP 可能需要串行地从自动机模型指令存储器中连续访问多次,也可能向"下阶段状态队列中"写回多个状态。这一部分内容将在3.2.2中详细介绍。

### 3.2.2 LAP 指令集

事实上,每一条 LAP 指令不仅编码了一个自动机状态的 ID(身份编码),也编码了该状态对应的类型和其他附加信息。LAP 的机器指令编码如图3.2所示。每条 LAP 机器指令包含 "Signature"、"Target"、"Type"、"Accept"和"Attach"五个域,共计 32 个比特。其中,"Signature"域是每条指令的指纹,用于检验该条指令是否是一条有效指令。之所以需要设立这一个域,是因为 LAP 会重叠的存储每个状态的状态切换表,每个状态可能会取到一条不属于该状态的指令。设立这样一个域,可以在每个状态取到不属于自己的指令时采取特殊的应对措施。"Target"域则是编码了目标状态的身份编码。在 LAP 中,每个自动机状态被编码成 12 个比特。因此,在本文的实现中,每个 LAP 核心支持最多 4096 个不同的自动机状态。"Type"域则是定义了目标状态的类型。在本文中,总共支持 7 种自动机类型。事实上,我们正是按照"Type"域将 LAP 指令划分成 7 类。LAP 的"Type"域就类似于 RISC 指令中的 OpCode(指令类型)。"Accept"域只有 1 比特,用来指示该状态是否是接受态。如果当前状态的"Accept"域值为 1,LAP 将向宿主CPU 汇报该接受态。最后,8 比特的"Attach"域是附加信息。对于不同类型的状态类型,"Attach 域"的值有着不同的解释和用法。

| 指令格式                                    |        |      |          |        |  |

|-----------------------------------------|--------|------|----------|--------|--|

| Transition Primitive Instruction Format |        |      |          |        |  |

| Signature                               | Target | Type | Accepted | Attach |  |

| 8bit                                    | 12bit  | 3bit | 1bit     | 8bit   |  |

图 3.2 LAP 的指令格式

我们参考 UAP<sup>[27]</sup> 和 UDP<sup>[28]</sup> 这两款处理器的指令集,设计了 LAP 指令集。 表格3.1展示了 LAP 支持的指令类型和功能描述。为了支持 NFA、DFA 和 ADFA 模型, LAP 总共支持 7 条指令,也就是支持 7 种类型的自动机状态。事实上,在 后续章节3.3.3还会提出对这些指令的进一步优化。接下来,本文将会分类介绍这些指令所对应的自动机状态的执行细节 (从该状态被 LAP 从"当前阶段状态队列"中取出到该状态执行结束)。我们将使用伪代码的形式展现这些过程,此处做一些约定:

- 参考图3.1, 我们用 CSQ(Current Stage Queue) 代指当前阶段状态队列,并使用 NSQ(Next Stage Queue) 代指下阶段状态队列。对于这两个队列,我们可以从队列头取出一个状态(pop())或者向队列尾存入一个状态(push())。

- 所有涉及到对指令存储器进行访问的操作都使用红色字体标识出来。 Mem[Addr] 代表读取指令存储器地址为 Addr 处的指令。

- signature\_check(input\_char,Instruction1.signature) 函数的作用是对取出来的指令 Instruction1 的 signature 域和当前输入字符进行比较。如果检验通过,说明 Instruction1 是一条有效指令。否则,取出来的指令是无效的。准确来说,这条指令不属于当前状态。详情请参看3.5.2。

- Execute(Instruction2) 函数是指:不将 Instruction2 写入 NSQ,而直接将该指令转化为对应的自动机状态,并立即执行该状态。被执行的状态可以属于以下介绍的任何类型。该函数被调用时就相当于嵌套的立即调用以下介绍的6个算法之一。这也意味着,这条指令的执行过程需要多个连续的周期。

- assert() 是用来终止当前算法的执行的,如果断言不被满足。使用此函数是想说明,以下介绍的6个算法会针对特定的状态类型被选择性的调用。

| 指令类型            | 功能描述                                |

|-----------------|-------------------------------------|

| NULL            | 空指令,在接受任何输入字符时不产生任何操作               |

| BASIC           | 基本指令,实现 DFA 模型中带标签的状态切换             |

| EPSILON         | 支持 NFA 模型,执行时可能会写回多个下阶段状态           |

| PERSIST         | 优化 NFA 执行,将当前状态立即写回下阶段状态            |

| DEFAULT_BASIC   | 支持 ADFA 模型,实现基础的 default transition |

| DEFAULT_CASCADE | 支持 ADFA 模型,实现级联的 default transition |

| MAJORITY        | 压缩自动机状态的出边数目,实现模型压缩                 |

表 3.1 LAP 支持的 7 条指令和它们的功能描述

#### 1. 支持 DFA 模型

DFA 模型中的每个状态都会被实现为 BASIC 类型。同时,BASIC 状态也被用在 NFA 和各类衍生的动机模型中。这类状态只包含若干条向外的 labeled edge。如算法3.1所示,当前状态首先从当前阶段状态队列中被取出。如果经检测,该状态是 BASIC 类型状态,则继续处理。首先,我们需要从指令存储器中取出一条指令 Instruction1。指令的地址是通过当前状态的 Target 域也就是其状态编号

和当前输入计算出来的。此处的地址计算非常简单,这得益于编译算法3.5.2的巧妙安排。如果当前 Instruction1 的指纹检测通过,则说明这是一条有效指令。随后,该指令将被转化为对应的状态并写回 NSQ。否则,当前状态在当前输入下没有对应的有效出边。此时,LAP 不写回任何状态直接结束当前状态的处理。

#### 算法 3.1 BASIC 状态的执行算法

- 1 current\_state = CSQ.pop();

- 2 assert(current state.Type==BASIC);

- 3 Intruction1 = Mem[current state.Target + input char];

- 4 **if** signature\_check(input\_char,Instruction1.signature)==True **then**

- 5 NSQ.push(Intruction1);

- 6 end

### 2. 支持 NFA 模型

为了支持 NFA 模型,需要增加一种新状态类型: EPSILON 类型。DFA 模型的状态转移函数  $\delta(q,a)$  在接受输入 a 时只会最多一个状态。此过程,可以使用BASIC 状态实现。而 NFA 模型的  $\delta(q,a)$  在接受输入 a 时可能会连续激活多个状态。在本文,我们实现 NFA 模型的方式是实现 NFA 模型中特有的一种边:  $\epsilon$  边 (见第2.1.2小节)。EPSILON 类型状态,除了进行类似于 BASIC 类型的状态转换外,还会额外执行另一个状态( $\epsilon$  边指向的状态)。如算法3.2所示,代码 1-5 行的操作和3.1是一样的。然而,在此之后,EPSILON 状态会进行第二次对指令存储器的读取。使用的地址,是编码在 LAP 指令的 "Attach"域的值。随后,立即解析出该指令包含的状态并立即执行该状态。值得注意的是,如果  $\epsilon$  边指向的状态仍然是 EPSILON 状态,则可能会嵌套执行多个 EPSILON 状态。通过这样的方式,一个状态可以连续地激活 1 到无穷个状态,从而实现 NFA 的状态转移特性。

#### 算法 3.2 EPSILON 状态的执行算法

- 1 current\_state = CSQ.pop();

- 2 assert(current state.Type==EPSILON);

- 3 Intruction1 = Mem[current state.Target + input char];

- $\textbf{4} \ \ \textbf{if} \ signature\_check(input\_char,Instruction1.signature) == True \ \textbf{then} \\$

- 5 NSQ.push(Intruction1);

- 6 Intruction2 = Mem[current state.Attach];

- 7 Execute(Intruction2);

- 8 end

除此以外,PERSIST 类型状态是为了优化 NFA 的处理性能。NFA 模型中有一类状态一旦激活就永远不会失活。这类状态在 NFA 的状态转移图中有一个典型的特征:有一条  $\epsilon$  出边指向自己。NFA 自动机的初始状态往往就是这样的

PERSIST 类型。我们也可以使用 EPSILON 类型实现这样的结构。然而,这将使得我们需要嵌套调用两次 EPSILON 执行算法。事实上,如果我们已经知道某  $\epsilon$  边的目的地正是当前状态自身,我们可以避免第二次存储器访问,直接将当前状态写回下阶段状态队列。如算法3.3所示,伪代码 1-5 行的操作类似于 EPSILON 状态的操作。然而,在此之后,PERSIST 状态在执行时,不需要进行第二次指令存储器访问,也无需嵌套的执行 EPSILON 状态。它直接将当前状态写回 NSQ。

### 算法 3.3 PERSIST 状态的执行算法

- 1 current\_state = CSQ.pop();

- 2 assert(current state.Type==PERSIST);

- 3 Intruction1 = Mem[current state.Target + input char];

- 4 **if** signature check(input char,Instruction1.signature)==True **then**

- 5 NSQ.push(Intruction1);

- 6 end

- 7 NSQ.push(current state);

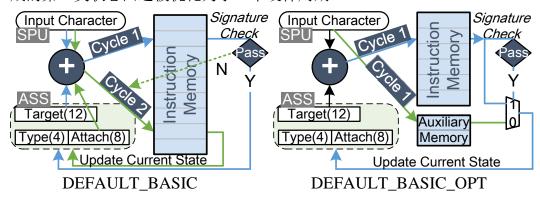

#### 3. 支持 ADFA 模型

为了支持 ADFA 模型,我们需要提供对 default transition (默认状态转换) 的支持。为了优化性能,我们在 LAP 中实现了两类对 default transition 的支持。

我们为此引入的第一类新状态为 DEFAULT\_BASIC。DEFAULT\_BASIC 状态在自动机状态转移图中的特征为:它有一个默认状态,但是它的默认状态是BASIC类型(不包含默认状态)。该类状态的执行过程如算法3.4所示。伪代码的1-3行是常规操作。如果 DEFAULT\_BASIC 状态取出的指令 Instruction1 通过了指纹检测,那么该类型状态的后续操作和 BASIC 类型一致,直接将 Instruction1 编码的状态写回 NSQ。如果指纹检测失败,LAP将从 DEFAULT\_BASIC 状态的默认状态中查找相应的边(关于 ADFA 模型,请参考第2.1.5小节)。由于 DEFAULT\_BASIC 状态的默认状态一定是 BASIC 类型,我们可以直接利用该 BASIC 状态的 Target 域和当前输入字符计算出新地址重新进行新指令的读取。如代码的第 7 行所示,DEFAULT\_BASIC 类型在被编码时,它的 Attach 域存储的就是其默认状态的 Target 域。因此,第 7 行代码可以在 DEFAULT\_BASIC 类型状态取得拥有错误指纹的指令后,进行第二次指令获取。最后,我们将第二次访存获得的有效状态写回 NSQ。

第二类新状态为 DEFAULT\_CASCADE 类型。DEFAULT\_CASCADE 状态是 DEFAULT\_BASIC 状态的推广。理论上,我么可以用 DEFAULT\_CASCADE 实现 DEFAULT\_BASIC,但是性能上将有所降低。DEFAULT\_CASCADE 状态和 DEFAULT\_BASIC 状态在自动机状态转换图上直观的区别是,DEFAULT\_CASCADE 状态的默认状态本身也一定拥有一个默认状态。也就是说,假设  $S_0$  属于 DEFAULT\_CASCADE

#### 算法 3.4 DEFAULT BASIC 状态的执行算法

```

current_state = CSQ.pop();

sassert(current_state.Type==DEFAULT_BASIC);

Intruction1 = Mem[current_state.Target + input_char];

if signature_check(input_char,Instruction1.signature) == True then

NSQ.push(Intruction1);

else

Intruction2 = Mem[current_state.Attach + input_char];

NSQ.push(Intruction2);

end

```

FAULT\_CASCADE 类型,那么一定存在一个  $S_1$  是  $S_0$  的默认状态,而且还存在一个  $S_2$  是  $S_1$  的默认状态。DEFAULT\_CASCADE 类型状态的执行过程如算法3.5所示。该算法和3.4的执行过程类似,二者区别主要在 7-8 行伪代码。由于在执行 DEFAULT\_CASCADE 状态时,我们无法得知其默认状态的类型。我们需要首先读取一条指令,该指令编码了其默认状态的信息。随后,我们直接执行该默认状态。如果该默认状态还是 DEFAULT\_CASCADE 状态,那么重新调用该算法。通过这种方式,我们可以实现 ADFA 模型中的连续的 default transition。

#### 算法 3.5 DEFAULT CASCADE 状态的执行算法

#### 4. 其他指令

ADFA 模型中的 default transition 可以消除状态间的冗余边,而 majority transition 则是为了消除每个状态内部的冗余边。正则表达式支持字符范围的识别,比如 [a-z] 可以接受 "a" 到 "z"之间 26 个字符中的任意一个,而 [^a] 接受除了 "a"以外的任意字符。因此,如果实现为 BASIC 类型转态,那么该状态有 26 条出边([a-z])或者 255 条出边([^a])。但是这些边都有一个相同的目标状态,被称为 MAJORITY 状态。因此,我们引入 MAJORITY 类型的状态。该类状态拥有一个 majority 边,指向他们的 MAJORITY 状态,也就是大部分情况下会切换到的

目标状态。如算法3.6所示,代码 1-5 行和 BASIC 类型一致。当 MAJORITY 状态根据当前输入字符取得的是有效状态(指纹检测通过),则将该状态写入 NSQ。但是,如果取得的是无效指令时,LAP 则将 MAJORITY 状态写入 NSQ(如代码7-8 行所示)。通过支持 MAJORITY 状态,可以实现更紧致的自动机模型,进一步减少自动机模型对存储器的空间占用。

#### 算法 3.6 MAJORITY 状态的执行算法

9 end

# 3.3 LAP 指令集优化

在本节,我们首先分析 ADFA 模型在模型压缩方面展现出的显著效果。随后,我们分析使用 ADFA 模型后模式匹配的性能下降的根本原因。最终,我们结合 ADFA 模型的特点,提出了两条新的机器指令。使用这两条指令,我们可以实现更高效的 ADFA 的执行。在这一过程中,我们改变了原本的 ADFA 的执行算法,同时也改变了底层硬件的设计。采用这样一种软硬件协同的设计方式,我们将可以实现更快的基于 ADFA 模型的模式匹配计算。

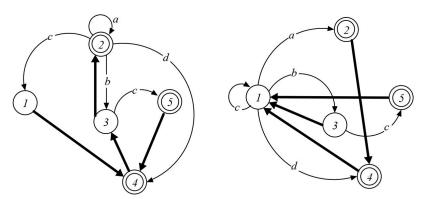

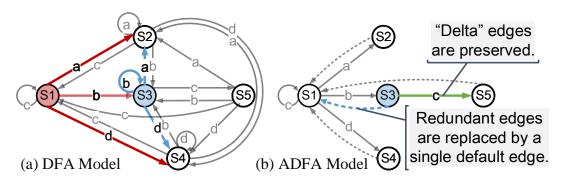

# 3.3.1 ADFA 对自动机模型的高效压缩

第2.1.5小节详细介绍了 ADFA 模型。图3.3则展示了接受相同正则表达式集合的 DFA 模型与 ADFA 模型。ADFA 模型通过增量存储的方式消除了大量的边,从而极大地压缩了模型的体积。从图3.3(a) 中的红线和蓝线我们可以发现,S3 和S1 在接受相同的输入"a","b"或者"d"时,会跳转到相同的状态。这就是ADFA 模型试图利用的"状态间的冗余性"。在图3.3(b) 中,S3 中添加了一条新的 default edge 指向 S1(通过虚线表示),同时删除了 S3 中的冗余边。

在 S3 中引入 default edge, 这对于 DFA 模型的大小的影响还可以从图3.4中看出。该图清晰地展示了在引入 default edge 前后 Transition Table (状态转移表)的变化。此处先解释下,对于模式匹配任务,待匹配的模式通常是以正则表达式

图 3.3 DFA 与等价的 ADFA 模型的状态转换图

的形式作为输入。这些正则表达式会被转换为对应的自动机模型:不同的正则表达式会产生不同状态数目和连接关系的自动机模型。无论是基于通用处理器还是专用处理器,我们都需要存储该自动机模型。本文使用类似状态转移表的形式,存储自动机状态和状态间的连接关系。因此,状态转移表的大小就是我们实际在存储自动机模型时需要的存储器大小。可以从图3.4中看到,假设输入字符集合为  $\Sigma = \{a,b,c,d\}$ ,那么为了存储状态 S1 和 S3 我们总共需要存储 8 个表项。S3 和 S1 之间边的冗余性可以从他们的状态转移表中直观的看出: S3 和 S1 的状态转移表的第 1、第 2 和第 4 行的内容是一样的。在引入 ADFA 模型的default edge 后,S3 中 3/4 的表项可以被删除。事实上,实际的输入字符集合通常是 ASCII 码,也就是说  $|\Sigma| = 256$ 。此时每个状态有 256 个表项,default edge的引入可以获得更大的收益。

|     | S1's Default Edge S3's |                  |  |  |

|-----|------------------------|------------------|--|--|

|     | Transition Table       | Transition Table |  |  |

| ʻa' | S2                     | <del>\$2</del>   |  |  |

| ʻb' | S3                     | <b>S3</b>        |  |  |

| 'c' | S1                     | S5               |  |  |

| 'd' | S4                     | <del>\$4</del>   |  |  |

图 3.4 ADFA 模型对状态转换表的压缩

#### 3.3.2 ADFA 降低模式匹配速度的根本原因

ADFA 模型也引入了更复杂的运行时操作(状态回退),从而导致了性能的 损失。在 DFA 模型中,为了处理一个输入字符,我们只需要对状态跳转表进行一次内存访问。每当处理一个新的输入字符时,我们从当前状态的跳转表中读取一个表项,该表项编码了下一个状态的信息。然而对于 ADFA 模型来说,情况却有所不同。ADFA 模型使用了增量存储,每个状态的冗余边被去除了。这引进了一个新的计算需求:我们需要在运行时进行"fall-back"(状态回退)。一旦当前

状态需要得知一条已经被去除的冗余边的目的地,我们需要从当前状态的默认状态处获得这样的信息。因此,当前状态需要首先回退到它的默认状态,并且基于这个新状态(其默认状态)重新处理当前输入字符。比如,我们假设图3.3中的S3是当前状态,而当前输入字符是"b"。我们可以发现,(b)图中S3并没有一条标签为"b"的有效边。这是因为,这条边作为冗余的边被删除了。因此,在实际执行时,S3需要首先回退到它的默认状态S1。随后,我们试图从S1的状态转移表中查找我们需要的边。这需要引入额外的对指令存储器的访问,因为我们需要额外访问S1的状态转移表。如果出现了多次连续的状态回退,我们可能需要更多的指令存储器访问。因此,额外的存储器访问被"fall-backs"引发。这降低了已有硬件方案基于ADFA模型的模式匹配速度。

# 3.3.3 ADFA 降低模式匹配速度的优化思路

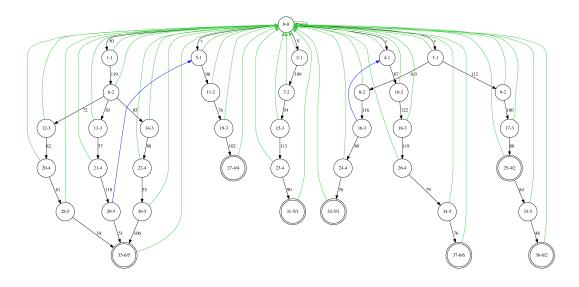

基于以上分析和对 ADFA 模型的拓扑关系的分析,我们得出以下的核心优化思路。既然状态回退会降低 ADFA 的处理速度,那么我们如何更快的实现状态回退呢?图3.5展示了 ADFA 模型在实际的工作负载下的典型拓扑结构。相比于之前展示 ADFA 模型(如图3.3),图3.5中的 ADFA 结构更符合实际的工作负载。(该图为矢量图,可能需要一定时间加载。加载完成之前,图片可能显得比较模糊;加载完成后,图3.5会很清晰。)该图展示的 ADFA 模型接受以下的正则表达式:

- Vm6qZ

- rpdP(T0)?

- rgtPL

- vbLf

- 2w(HRQ6|UX7j|S9v3)

- tWzwOL

图3.5需要从两个层次来观察。首先,我们观察由黑色的边(labeled transition)和各状态节点组成的类似树状结构。该树状结构的根节点是 ADFA 模型的初始节点。值得一提的是,如果按照本文的参数(见第3.5小节)进行 ADFA 模型构建,则有且只有一个根节点。从根节点出发,如果当前输入字符序列符合某个我们预期的正则表达式,那么当前状态会沿着该树状结构一直往下走(随着字符的不断输入,当前状态会不断的切换)。如果走到了最底部的双圆圈节点(接受态),则说明发现了符合一到多个正则表达式的输入子序列。同时,图3.5中绿色和蓝色的边代表着 ADFA 模型中的 default transition。这些边和状态节点共同组成了 ADFA 模型的第二个层次。在当前状态从初始节点沿着某个路径一直往下走时,可能在某个地方突然不再匹配正在匹配的某个模式。那么此时,当前状态

图 3.5 ADFA 模型的典型拓扑结构

在当前输入下不再有有效的出边。随后,该状态将会沿着绿色或者蓝色的边进 行状态回退。值得注意的是,沿着这种边进行回退时,当前输入字符是不被消耗 的。这也正是,状态回退会导致字符处理速度下降的根本原因。

此时,我们可以有一个直观感受: ADFA 模型在运行时,如果当前输入字符符合当前正在匹配的若干模式,当前状态会向下走,会走的更深。严谨来说,就是当前状态的深度(距离初始状态的最短距离)会随着匹配的过程不断增加。如果当前字符导致匹配到一半的模式发生了不匹配,那么当前状态会回退到深度更浅的地方。之所以回退过程中当前状态的深度一定会降低,是因为第2.1.5小节介绍过 ADFA 模型的一个约定: ADFA 模型中的 default edge 只会从深度更深的节点指向深度更浅的节点。

在图3.5中,我们将 default edge 划分成两类。第一类 default edge 我们使用绿色的边表示,这些边直接指向 ADFA 的初始状态。第二类 default edge 我们使用蓝色的边表示,这些边指向非初始节点。值得一提的是,更大规模的更贴近现实的正则表达式集合对应的 ADFA 模型的基本结构和图3.5类似,但是第二类default edge 的占比会相应提高。通过分析 ADFA 模型的状态间的拓扑结构,我们可以发现每个状态很容易发生状态回退。这是因为在当前状态下,当前输入必须等于当前状态下存在的某条出边的 label。而一旦发生第一类回退,当前状态会立即回退到初始状态。而如果发生第二类回退,也很有可能最终连续回退到初始状态。因此,优化针对 ADFA 模型中初始状态的回退(第一类回退)成为最关键的优化方向。同时,第二类回退随着正则表达式规模的增加比例也会增加。因此,如何高效的进行第二类状态回退也是一个值得关注的优化方向。

# 3.3.4 并行化的 ADFA 执行算法与新的机器指令

第3.3.2小节已经分析了 ADFA 模型性能下降的根本原因:运行时要进行状态回退。同时,第3.3.3小节也分析了我们应该关注的两个优化方向:优化第一类状态回退和第二类状态回退。本节将从指令集和硬件执行模型的角度提出具体的优化方案。

按照旧的硬件执行模型(见第3.1小节),一个硬件周期最多可以进行一次对指令存储器的读取。同时,ADFA模型的第一类回退是通过前文介绍过的DEFAULT\_BASIC(算法3.4)状态类型实现,而第二类回退是通过前文介绍过的DEFAULT\_CASCADE状态类型(算法3.5)实现。通过分析这两个算法我们可以发现,他们都需要进行多次指令存储器访问。因此,为了实现更快的状态回退,我们需要尽可能并行化这些对指令存储器的访问。为了实现这个目的,我们需要做两件事:第一,拓展原本的硬件执行模型,使得指令存储器支持并行的读取(一个周期读取多条指令);第二,优化原本的ADFA执行算法,使得其内部的存储器访问和其他操作尽可能并行化。

# 1. 针对第一类状态回退的优化指令: DEFAULT BASIC OPT

我们已经观察到,ADFA 的初始状态的状态转换表会被频繁的访问,无论是因为正常的状态切换还是因为状态回退。因此,我们此处试图通过并行访存的方式掩盖对初始状态的转态转换表的访问开销。图3.6左侧展示了未优化的DEFAULT\_BASIC 状态类型的执行流程。前文中算法3.4描述了该过程。如蓝色线条所示,一条 LAP 指令在第一个周期被读取。如果这条指令字通过了指纹检测,它将会被用于更新当前状态。但如果指纹检测失败了,则需要额外进行一次针对 ADFA 初始状态的状态转换表的内存访问。比如,假设当前状态是图3.3中的 S3 而当前输入字符是"b"。那么 LAP 会首先将当前状态回退到状态 S1,然后在第二个硬件周期从 S1 的状态转换表中读取我们需要的那条被标为"b"的边。总的来说,对第二条指令的读取是可选的,这取决于第一条指令的指纹检测是否通过。这一依赖使得我们只能串行处理这两次内存访问。

幸运的是,这样的依赖是可以被打破的。如图3.6右侧所示,我们拓展了原本的硬件执行模型。在原本的主要的指令存储器之外,我们增加了一个很小的辅助存储器(Auxiliary Memory)。从而,我们每个硬件周期可以从指令存储器和辅助存储器中各自读取一条指令。DEFAULT\_BASIC\_OPT 状态并不会可选性的启动第二次存储器访问。相反的,优化后的指令并行的读取这两条指令,而不考虑第二条指令是否会用得上。由于该存储器很小,因此带来的额外开销很小。随后,LAP 根据对第一条指令的指纹检测结果选择这两条指令中的一条进行后续的处理。通过这种方式,这两条指令的读取被并行化,原本需要两个硬件周期才能完

成的第一类状态回退被优化为了1个硬件周期。

图 3.6 第一类状态回退的优化方案

对应的, DEFAULT BASIC OPT 的执行算法如算法3.7所示。

#### 算法 3.7 DEFAULT BASIC OPT 状态的执行算法

- 1 current\_state = CSQ.pop();

- 2 assert(current state.Type==DEFAULT BASIC OPT);

- 3 ///////Parallel Memory Access Begin///////;

- 4 Intruction1 = TransitionMem[current state.Target + input char];

- 5 Intruction2 = AuxiliaryMem[256 + input char];

- 6 ///////Parallel Memory Access End////////;

- 7 **if** signature check(input char,Instruction1.signature)==True **then**

- 8 NSQ.push(Intruction1);

- 9 else

- NSQ.push(Intruction2);

- 11 end

# 2. 针对第二类状态回退的优化指令: DEFAULT CASCADE OPT

第二类回退的执行流程与第一类回退截然不同。第二类回退的目标状态都有其自己的 default state。因此,这些状态的冗余边已经被 default edge 替代而且他们的状态转移表是不完整的。如果我们仍然使用第一类状态回退的优化方式,并行的访问他们状态转移表是没有意义的。因为,从它们的状态转移表中读取的指令可能仍然是无效指令。

但是,DEFAULT\_CASCADE 状态类型也是可以被优化的。不同于第一类状态回退,第二类状态回退的目标状态的状态类型是未知的。目标状态的类型可以是仍然是 DEFAULT\_CASCADE 状态类型也可以是 DEFAULT\_BASIC。因此,在我们回退到目标状态前,我们需要获得目标状态的完整信息(Target、Type 和 Attach)。这么多的信息是无法存储在当前状态的 attach 域的。因此,我们使用一条完整的 LAP 指令(本文称之为"附属指令")去存储第二类回退的目标状态

的完整信息,而当前状态的 attach 域则被用于去寻址这一条指令。因此,如果读取的第一条指令的指纹是错误的,我们则需要读取第二条指令。也就是说,第二条指令得读取是可选的(取决于第一条指令的 signature),而且第二条指令的读取发生在第二个机器周期。图3.7左侧展示了未优化前第二类状态回退的执行流程,该过程在算法3.5中也有所描述。我们观察到,附属指令通常在前一条指令(被附属的指令)执行结束后立即被读取。因此,我们把附属指令与其他指令分离开,并存放在辅助存储器中。通过这样的方式,我们可以在前一条指令还在访问主指令存储器的同时从辅助存储器中读取该条指令的附属指令。如图3.7右侧所示,这项优化通过 LAP 指令 DEFAULT\_CASCADE\_OPT 实现。通过利用辅助存储器的空闲带宽,我们掩盖了读取附属指令的存储器访问开销。通过这样的方式,我们将原本两个周期才能完成的第二类状态回退优化为1个周期完成。值得一提的是,虽然第二类状态回退只需要一个周期即可完成,但是这个周期是不会消耗任何输入字符的。因此,第二类状态回退仍然会使得 ADFA 模型的执行速度比不上 DFA 模型。

图 3.7 第二类状态回退的优化方案

对应的,DEFAULT CASCADE OPT 的执行算法如算法3.8所示。

# 3.4 LAP 的微体系结构

基于第3.2.1小节介绍的硬件执行模型和优化 AFDA 时进行的硬件执行模型的拓展(3.3.3),本节将详细介绍 LAP 的微体系结构。我们将首先介绍 LAP 的核心部件和流水线设计。随后,我们将介绍细粒度多线程技术在 LAP 中的应用。

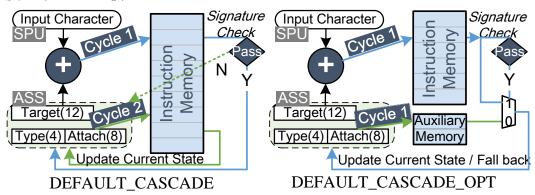

# 3.4.1 四级流水线架构

正如前文2.1所介绍的,自动机的执行开始于单个活跃状态 q0。在我们的实现方案中,每一个状态  $q \in Q$  被赋予了一个 12 比特的状态编码。同时,每一个输入字符  $\alpha in \Sigma$  是一个 8 比特的 ASCII 码字符。随着第一个字符输入自动机,q0

#### 算法 3.8 DEFAULT CASCADE OPT 状态的执行算法

根据状态转移函数  $\delta(q,\alpha)$  切换为 1 或者多个活跃状态。自此之后,每当有一个字符被输入自动机,每一个活跃状态根据状态转移函数  $\delta(q,\alpha)$  独立地切换到另外一组新的状态。为了在硬件上运行自动机模型,我们需要用硬件记录在整个自动机执行过程中每一时刻的所有活跃状态,同时周期性的进行状态的切换。

#### LAP 包含以下核心部件:

11 end

- 在 LAP 中,我们把所有的自动机活跃状态存储在**活跃状态栈 (Active State Stack, ASS)** 中,并且动态的更新 ASS 中存储的内容。为了支持 ADFA、DFA 和 NFA 模型,ASS 可以同时存储多个活跃状态并且串行的输出这些状态。因此,NFA 中每一个活跃状态的状态切换过程可以轮流执行。

- 输入流预取部件(Stream Prefetch Unit, SPU)的作用是从输入字符缓存 (Input Buffer)中加载输入数据。LAP 的输入数据是一串字符流,其中每个字符都定义在 Σ 中。SPU 串行的从字符流中顺序的输出每个字符;而且SPU 只会在当前字符已经被彻底被自动机处理掉后才会输出新的字符。输出一个字符后,SPU 内部的指向数据流的指针会自增。

- 主指令存储器和辅助存储器(Instruction Memory and Auxiliary Memory)存储 LAP 的二进制程序。LAP 的二进制程序由前文提到的 LAP 指令集 (3.2.2) 构成。这两个基于 SRAM 的存储器存储着整个自动机模型的状态节点和节点间的拓扑关系,从而描述了自动机模型的整体行为。值得一提的是,LAP 的二进制程序是根据我们要匹配的正则表达式集合和要使用的自动机模型生成的。当要匹配的模式发生改变时,我们需要重新编译 LAP 的二进制程序并写入这两个存储器。

- 指令译码器(Instruction Decoder)是 LAP 的主控制器。该控制器是纯粹的组合逻辑,负责收集其他部件的输出信息去更新 ASS 的内容或者去汇报被激活的接受态  $q \in F$ 。

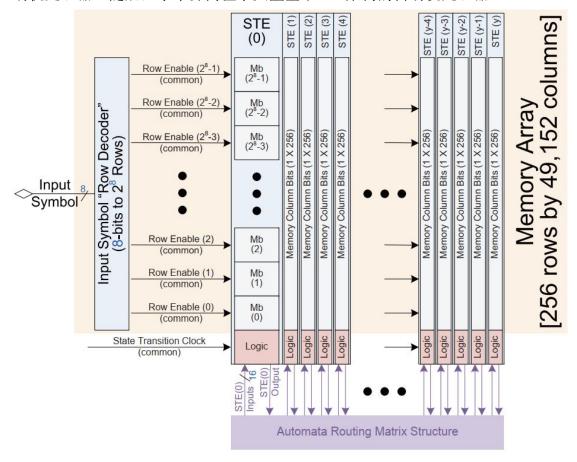

为了在 FPGA 和 ASIC 平台上实现较高的硬件主频,我们为 LAP 设计了四级的流水线架构。图3.8展示了 LAP 简化的硬件结构。如果所示,LAP 的数据通路被分割成了 4 个阶段。

- 第一阶段, ASS 输出一个活跃状态(当前状态); 同时, SPU 输出一个字符(当前输入字符)。

- 第二阶段, LAP 根据当前状态和当前输入计算出两个物理地址。通过编译器的精心布局,要读取的指令的地址可以通过很简单的操作(图3.8中所示的整数加法)计算出来。

- 第三阶段, 两条指令被并行的读取。

- 第四阶段,指令译码器更新 ASS 并且向外部汇报当前状态的编码(如果当前状态 q 是接受态,即  $q \in F$ )。

图 3.8 LAP 的四级流水线架构

通过实验证明,该流水线的设计和流水级的划分是合理的。我们在 FPGA 平台上综合实现 LAP 的时候, LAP 的每个阶段的电路延迟是均衡的。

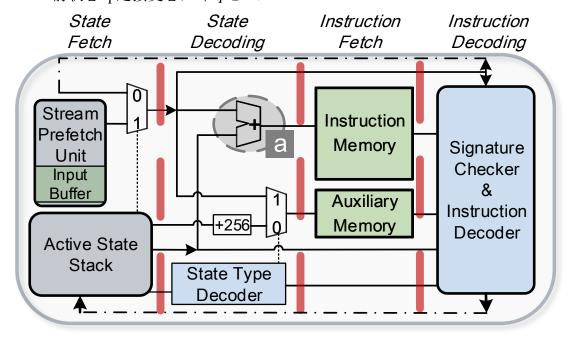

#### 3.4.2 细粒度多线程

我们将细粒度多线程技术<sup>[45]</sup> 运用到了 LAP 的微架构中,从而消除了 LAP 流水线中的相关性。通过在 LAP 的流水线中填充四个完全不相关的线程,LAP 的流水线不会出现任何停顿,也实现了最大化的流水线吞吐。图3.9是 LAP 在多线程模式下工作时的硬件部件时空图。其中,纵轴是 LAP 硬件流水线的四个阶段,横轴是当前所处的机器周期编号。从图中可以看出,LAP 的四个流水级可以填充 4 个不同的线程。这四条线程的指令轮流从 SF 阶段被发射。比如,第 0

个周期我们发射了线程 1 的指令,第 1 个周期则发射线程 2 的指令。如图3.9中虚线所示,每个线程内部的指令都有数据和控制相关。然而,由于相同线程中的指令每 4 个周期才能发射一次。相同线程的指令都相隔了 4 个周期发射,因此他们的数据和控制相关不会引起任何问题(后一条指令会在前一条指令完成后再发射)。因此,通过细粒度多线程技术,我们避免了复杂的流水线冲突处理。同时,不同线程的指令之间不存在任何数据和控制相关。因此,LAP 的流水线是Stall-Free(无停顿)的。值得注意的是,在 LAP 中每一个线程都有自己独享的输入字符流。这意味着,LAP 每个线程独立的处理一个输入字符流。另一方面,LAP 所有的线程需要共享同一个 LAP 二进制程序。因此,LAP 将同时从四个输入流中查找相同的一组预定义模式(正则表达式集合)。

为了使得 LAP 支持细粒度多线程,我们在 SF 阶段实现了一个 2 比特的硬件计数器。该计数器每个硬件周期自动加一。并且,该计数器的值(我们称之为Context ID, CID) 随着硬件流水线一级级向后传递。那么,LAP 的每一个流水级都有他们自己的 CID。在第一个流水级中,我们使用 CID 来选择要读取的输入字符流。同时,我们在 ASS 中存储了 4 个线程各自的机器状态,使用 CID 选择其中一组状态输出。总的来说,细粒度多线程技术可以显著地提高流水线的利用率,减少甚至避免流水线停顿。它带来的弊端则是,使得处理器单线程处理速度下降。然而,LAP 是一个面向高吞吐的计算负载而并不追求单线程计算能力。同时,多模式匹配的任务可以很容易的切分成多个部分并分配给不同的线程。因此,细粒度多线程成为了 LAP 用于解决流水线冲突的极佳选择。

图 3.9 细粒度多线程技术在 LAP 中的应用

# 3.5 编译算法设计与实现

为了在 LAP 上运行模式匹配任务,我们设计并实现了相应的编译软件。我们改编了开源的 C++ 软件<sup>[46]</sup> 用于将正则表达式编译成特定的自动机模型(一阶段编译)。同时,我们用 Python 语言开发了二阶段编译器。二阶段编译器可以根

据第一阶段生成的自动机模型,进一步生成 LAP 二进制代码。

# 3.5.1 将正则表达式集合转化为等价自动机模型

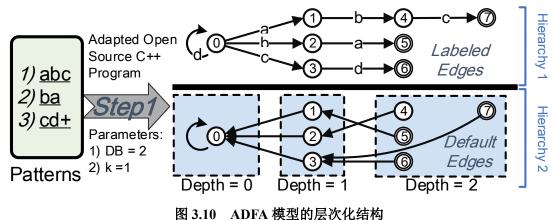

在本文,正则表达式可以被转换为 ADFA 模型或者 NFA 模型。图3.10就为这样的转换过程举了一个例子,并且层次化的展示了生成的 ADFA 模型。图中 labeled edges 用于表示指纹检测通过时会进行的状态转换,而 default edges 则是会在指纹检测失败时触发。值得一提的是,我们在生成 ADFA 模型时,将开源软件<sup>[46]</sup>中的一个重要参数"深度约束"(Depth Bound, DB)设置为 2。"DB"这个参数是用于在构建 ADFA 模型的时候约束最长的 default 路径,也就是图3.10中 hierarchy-2 的最长路径不能大于"DB"的值。通过这样的方式,我们可以保证每个状态最多经历两次状态回退就可以到达初始状态。更重要的是,这可以将"附属指令"(见第3.3.3小节)的数目约束在一个较小的值,从而保证"附属指令"只会占用辅助存储器很少的存储空间。

图 5.10 ADIA 快至的法认他知何

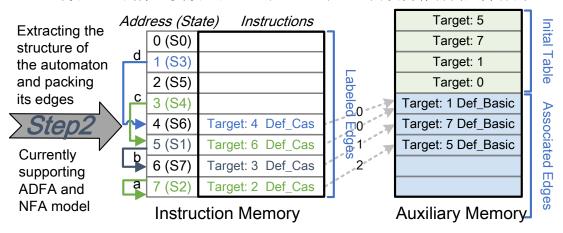

# 3.5.2 自动机模型的 Split EffCLiP 二进制表示

在LAP中,所有状态各自的状态转换表都利用高效的线性打包算法(Efficient Counpled-Linear Packing algorithm, EffCLiP<sup>[47]</sup>) 重叠的存储在 SRAM 中。通过这种重叠存储的方式,可以实现非常紧致的自动机模型的存储。同时,为了支持第3.3.3小节提出的优化方案,本文提出 Split EffCLiP 的表示方式,用于将自动机模型紧致的存储在两个分离的 SRAM 存储器中。如图3.11所示,图3.10中的 labeled edge 都被 EffCLiP 算法非常紧致的存储在线性的地址空间(Instruciton Memory)中。同时,为了支持对初始状态的查找表的并行访问,我们将初始状态的查找表(图中称为"Initial Table")存储在辅助存储器中。不仅如此,为了支持对"附属指令"的并行访问,我们也将这些附属指令分离出来并存储在辅助存储器中。

此处我们介绍下 Split EffCLiP 的二进制表示下,LAP 是如何进行访存和计算的。如图3.11所示,图的左边是使用 EffCLiP 重叠存储的各个自动状态的跳转

表;而图的右边则是平铺存储的 Initial State 的跳转表和用于编码 default state 完整信息的指令。该图存储了图3.10中所示的自动机模型。值得注意的是,我们为图3.10中的每个状态 S0-S7 赋予了一个新的状态编号。比如图中,S0 在 Split EffCLiP 中的编号为 0,S3 的编号为 1。

假设当前状态是图3.10中的 S3,那么当前状态的 Target 域值则为其编号 1。如果当前输入是 d, 那么我们可以计算出下一条指令的地址为 1+'d'(使用'd'的 ASCII 码值来做整数加法)。图中为了简化(否则我们需要画出有几十个表项的 Instruction Memory),我们把 S3 的下一个状态存放在地址为(1+'d')-'a'的位置,也就是 1+3 的位置处。据此,我们取出的指令为"Target:4, Type:Default\_CASCADE\_OPT,Attach:0"。事实上,该指令还包含了 Signature 域。同时,该指令的 Signature 一定是'd',也就是当前输入字符,因此可以通过 signature check。因此,以上过程中,我们完成了从 S3 跳转到 S6(Target: 4 等价于 S6)。

在 S6 状态("Target:4, Type:Default\_CASCADE\_OPT,Attach:0")下,假设当前输入字符是'a'。那么,下一条指令地址则为 4(4+'a'-'a')。而事实上,S6 状态在输入为'a' 时没有出边。因此,尽管我们可以根据该地址取出一条指令。该指令的 signature 域却是'd',不等于当前输入字符'a'。因此,指纹检测失败。随后,检测当前状态 S6 的属性。由于 S6 是 Default\_CASCADE\_OPT 类型,因此我们启动第二类状态回退 (如3.3.4所介绍的)。根据当前状态的 Attach 域,我们从Auxiliary Memory 中取出当前状态的 Default State 的完整编码(也就是 Target: 1,Type: Default\_BASIC\_Opt,对应了状态 S3)。在这样的过程中,我们实现了从状态 S6 到状态 S3 的第二类状态回退。在 LAP 中,这两次内存访问是并行的。

图 3.11 ADFA 模型的 Split EffCLiP 表示

# 3.6 实验与评估

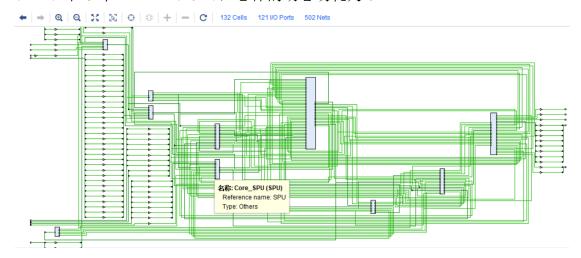

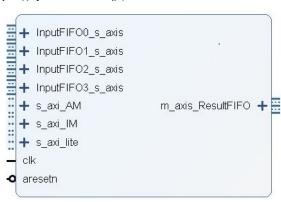

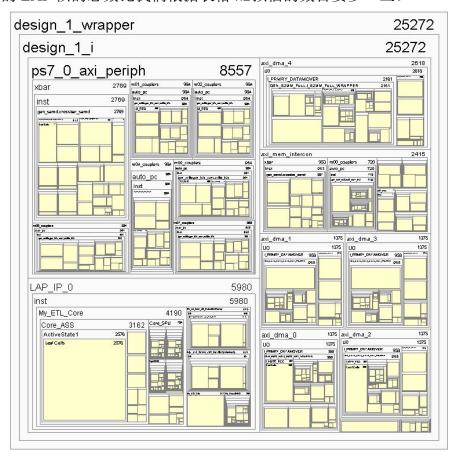

我们使用 Verilog 硬件描述语言实现了 LAP,并使用 Vivado 设计套件 2017 将 LAP 的原型以 263MHz 的主频部署(综合和实现)到了 Xilinx Artix-7 FGPA 上。图3.12展示了由 Vivado 集成开发工具自动生成的 LAP 原理图(Schematic)。图中显示了 LAP 的各个核心模块和模块接口,以及这些模块之间的电路连线。值得注意的是,图中不仅仅包括前文介绍的 ASS、SPU、Instruction Memory 和 Auxiliary Memory 等部件,还包括为了实现硬件流水线而设置的四级段寄存器。其中,主指令存储器(16KB)和辅助存储器(0.6KB)是通过 FPGA 上的 BRAM 资源实现的。总的来说,每一个 LAP 核心占用了 724 个 LUT(7%)、2199 个 FF(11%)和 5 个 BRAM(20%),总体的动态功耗为 0.12W。

图 3.12 LAP 在 Artix-7 FPGA 上的 Schematic

本文使用两类标准的工作负载用于 LAP 的评估。PowerEN simple<sup>[14]</sup> 是一系列标准数据集。它最早被 IBM 公司用于评估 PowerEN 处理器内部的正则表达式硬件加速器的性能。另外,Exact-Match(EM) 和 range1 是通过软件工具<sup>[46]</sup> 合成的工作负载。我们使用 line rate 这一指标来衡量 LAP 的处理速度,并使用 pattern density 去衡量 LAP 的存储效率。Line rate (symbol/cycle) 指示了每个 LAP 核心平均每个硬件周期可以处理的输入字符的数目。另一方面,pattern density(#patterns/KB) 是将待匹配的正则表达式的数目除以对应的自动机占用的存储器空间计算得来的。我们使用自己实现的编译软件将这些 workload 编译为对应的 LAP 二进制程序。随后,我们使用 Vivado Simulator 仿真这些程序在 LAP 上的执行过程。我们此处使用的 Vivado Simulator 是 Xilinx 官方提供的精确到每个硬件周期的仿真器,因此实验结果非常可信。总的来说,处理每个 workload 所用的硬件周期总数是通过观察 Vivado Simulator 的仿真波形图得出的数据,而pattern desity 则是由我们设计实现的编译器在编译过程中计算出来的。

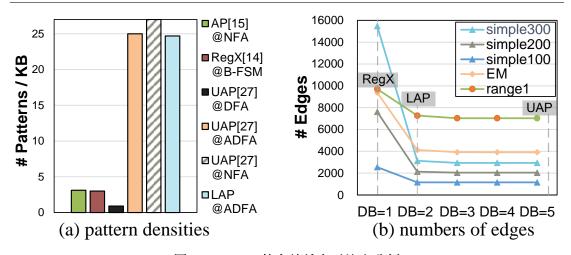

在展示 LAP 的各项性能指标时,我们对比了比较知名的相关工作。这些 工作包括: 芝加哥大学的 UAP<sup>[27]</sup>、IBM 的 RegX<sup>[14]</sup> 和 Micron 公司的 Automata Processor(AP)<sup>[15]</sup>。在评估 LAP 的处理速度时,我们比较的是 LAP、UAP 和 RegX 的单核心性能。LAP 单核心的硬件复杂度和 UAP 单核心类似,而且要比 RegX 单核心更轻量化。因此,比较它们的单核心性能是公平的。同时,我们选择了  $UAP^{[27]}$  一文中使用过的评价指标(line rate)来评价三款处理器的性能。我们使 用了 UAP<sup>[27]</sup> 一文中的实验结果和 RegX 处理器的理论最佳性能 (无 Cache Miss) 作为 LAP 的对照数据。值得注意的是,line rate 这一评价指标评估的是一个硬件 时钟周期内的平均吞吐,与具体的硬件平台无关。这使得本文提出的基于 FPGA 的 LAP 可以与基于 ASIC 平台的 UAP 和 RegX 进行公平的平台无关的比较。在 评估 LAP 的二进制代码存储效率时,我们使用了 UAP<sup>[27]</sup> 一文中相同的数据集 和评价指标进行评估。我们也从这篇文章中得知了 RegX 和 UAP 的存储效率。 Micron 公司的 AP 采用的是独热码的编码方式:每个 NFA 状态需要占用 256 比 特。因此,我们将 simple 400 正则表达式集合编译为对应的 NFA,并获取了生成 的 NFA 的状态总数。随后,我们通过二者之间的乘法(256 bits \* NFA 状态数) 计算出了 AP 的存储器空间占用。

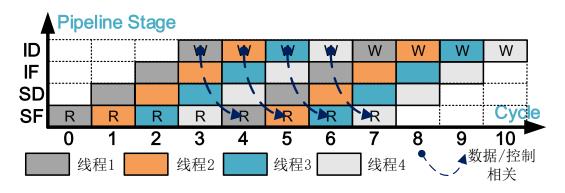

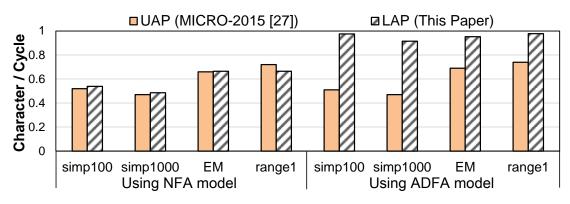

# 3.6.1 LAP 处理速度总览

图3.13展示了 LAP 的在不同的 workload 上整体的处理速度(line rate)。虽然我们的工作主要是为了实现更快的基于 ADFA 的计算,为了实现更为全面的性能评估,我们此处也评估了 LAP 基于 NFA 模型的性能。除此以外,UAP<sup>[27]</sup> 的性能也被包含在图中。LAP 和 UAP 使用类似的指令集,因此与 UAP 做直接的性能对比可以公平的展示本文提出的软硬件协同设计的有效性。如图3.13所示,LAP使用 NFA 模型时可以实现和 UAP 差不多的处理速度。(LAP 平均每个机器周期可以处理 0.49 到 0.66 个输入字符。)当使用 ADFA 模型时,LAP 在不同的工作负载上实现了 0.91 到 0.97 的 line rate。与之对应的,"ADFA 模型是一个更复杂的模型,因此每次状态转化需要更多顺序的存储器访问,因此产生了较低的 line rate,平均每个周期处理 0.47 到 0.75 个字符"(UAP<sup>[27]</sup>,2015)。总的来说,LAP在基于 ADFA 模型的模式匹配方面取得了显著的性能提升:相比于 UAP,在各个数据集上实现了 32% 到 91% 不等的速度提升。理论上,装备 5 个 LAP 核心的FPGA 原型系统基于 ADFA 模型可以实现 9.5Gbps 的处理吞吐。

图3.13中的原始数据如表格3.2所示。

图 3.13 LAP 在不同工作负载下的总体处理速度

表 3.2 LAP 在不同工作负载下的总体处理速度原始数据

|            | simple100 | simple1000 | EM    | rangel |

|------------|-----------|------------|-------|--------|

| UAP @ NFA  | 0.52      | 0.47       | 0.66  | 0.72   |

| UAP @ ADFA | 0.51      | 0.47       | 0.69  | 0.74   |

| LAP @ NFA  | 0.539     | 0.485      | 0.665 | 0.665  |

| LAP @ ADFA | 0.975     | 0.914      | 0.952 | 0.977  |

注:表格中数据的单位是 Character/Cycle

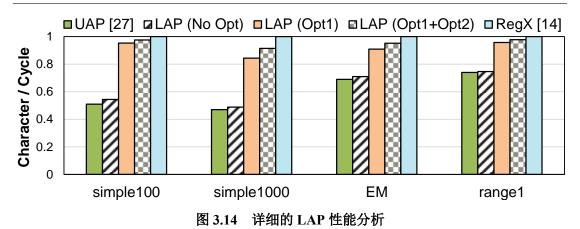

# 3.6.2 对 LAP 处理速度的详细评估

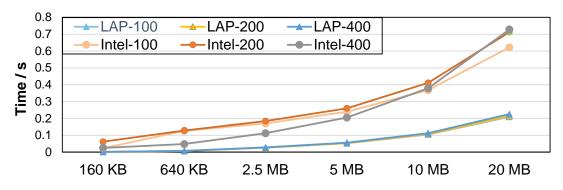

如第3.3.2小节所述,ADFA 模型所引发的额外的存储器访问导致了更慢的字符处理速度。因此,UAP<sup>[27]</sup> 系统基于 ADFA 模型进行模式匹配时处理速度较慢。相反的,RegX<sup>[14]</sup> 则实现了 DFA 模型下理想的字符处理速度。因此,我们在图3.14中将 LAP 的处理速度和这两款经典的基于 DFA 的硬件方案做对比。在图3.14中我们把 UAP 作为 baseline,而把 RegX 作为性能的天花板。通过这样的方式,读者可以直观的知道已有的基于 ADFA 的硬件方案已经达到了怎样的处理速度,同时也可以清晰地知道我们距离实现最理想的处理速度还有多远距离。同时,我们也评估了 LAP 在应用本文提出的优化 (见第3.3.3小节) 前后的性能提升,从而可以清晰地定位性能提升的源头。从图3.14中我们可以发现,LAP 在不使用任何优化的情况下和 UAP 的处理性能类似。然而,LAP 在使用第一项优化(优化第一类状态回退)后实现了显著地性能提升。这说明了限制 ADFA 处理速度的主要因素是第一类状态回退导致的额外存储器访问。更进一步,第二项优化(优化第二类状态回退)利用辅助存储器的空闲带宽进一步提升了 LAP 的字符处理速度。

图3.14中的原始数据如表格3.3所示。

表 3.3 详细的 LAP 性能分析原始数据

|                | simple100 | simple1000 | EM   | range1 |

|----------------|-----------|------------|------|--------|

| UAP            | 0.51      | 0.47       | 0.69 | 0.74   |

| LAP @NoOpt     | 0.54      | 0.49       | 0.71 | 0.74   |

| LAP @Opt1      | 0.95      | 0.84       | 0.91 | 0.96   |

| LAP @Opt1+Opt2 | 0.97      | 0.91       | 0.95 | 0.98   |